# COMPACT MODELS FOR INTEGRATED CIRCUIT DESIGN

SAMAR K. SAHA

## COMPACT MODELS FOR INTEGRATED CIRCUIT DESIGN

## COMPACT MODELS FOR INTEGRATED CIRCUIT DESIGN

CONVENTIONAL TRANSISTORS AND BEYOND

SAMAR K. SAHA

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2016 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works

Printed on acid-free paper Version Date: 20151014

International Standard Book Number-13: 978-1-4822-4066-5 (Hardback)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

The Open Access version of this book, available at https://doi.org/10.1201/b19117, has been made available under a Creative Commons Attribution-Non Commercial-No Derivatives 4.0 license.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

In loving memory of my parents, Mahamaya and Phani Bhusan Saha

## Contents

| Pre | face  |         |           |                                        | <b>xv</b> |

|-----|-------|---------|-----------|----------------------------------------|-----------|

| Au  | thor  |         |           |                                        | xix       |

|     |       |         |           |                                        |           |

| 1.  |       |         |           | pact Models                            |           |

|     | 1.1   | -       |           | els for Circuit Simulation             |           |

|     |       | 1.1.1   |           | ct Device Models                       |           |

|     |       | 1.1.2   |           | ct Interconnect Models                 |           |

|     | 1.2   |         | History o | f Compact Device Modeling              | 4         |

|     |       | 1.2.1   |           | istory of Compact MOSFET Modeling      |           |

|     |       | 1.2.2   |           | History of Compact MOSFET Modeling     | 7         |

|     |       |         | 1.2.2.1   |                                        |           |

|     |       |         |           | MOSFET Modeling                        | 7         |

|     |       |         | 1.2.2.2   | Surface Potential–Based Compact MOSFET |           |

|     |       |         |           | Modeling                               | 9         |

|     |       |         | 1.2.2.3   | Charge-Based Compact MOSFET Modeling   | 12        |

|     | 1.3   | Motiv   | ation for | Compact Modeling                       | 15        |

|     | 1.4   | Comp    | act Mode  | el Usage                               | 16        |

|     | 1.5   |         |           | el Standardization                     |           |

|     | 1.6   | Summ    | nary      |                                        | 17        |

|     | Exerc | cises   | -         |                                        | 18        |

|     |       |         |           |                                        |           |

| 2.  | Revi  | ew of E | Basic Dev | ice Physics                            | 19        |

|     | 2.1   |         |           |                                        |           |

|     | 2.2   | Semic   |           | Physics                                |           |

|     |       | 2.2.1   |           | Band Model                             |           |

|     |       | 2.2.2   |           | Statistics                             |           |

|     |       | 2.2.3   | Intrinsi  | c Semiconductors                       |           |

|     |       |         | 2.2.3.1   | Intrinsic Carrier Concentration        |           |

|     |       |         | 2.2.3.2   | Effective Mass of Electrons and Holes  | 25        |

|     |       | 2.2.4   | Extrins   | ic Semiconductors                      | 26        |

|     |       |         | 2.2.4.1   | Fermi Level in Extrinsic Semiconductor | 28        |

|     |       |         | 2.2.4.2   | Fermi Level in Degenerately Doped      |           |

|     |       |         |           | Semiconductor                          | 30        |

|     |       | 2.2.5   | Carrier   | Transport in Semiconductors            | 31        |

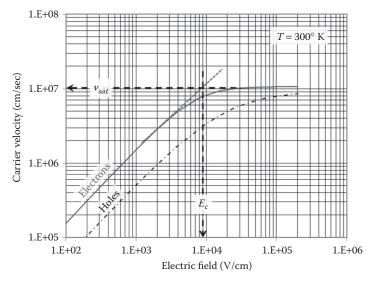

|     |       |         | 2.2.5.1   | Carrier Mobility and Drift Current     | 31        |

|     |       |         | 2.2.5.2   | Electrical Resistivity                 |           |

|     |       |         | 2.2.5.3   | Sheet Resistance                       | 34        |

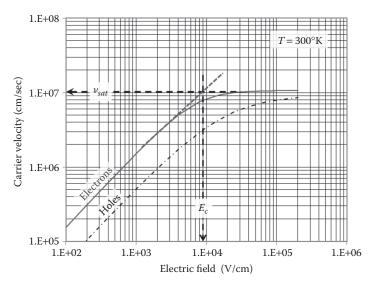

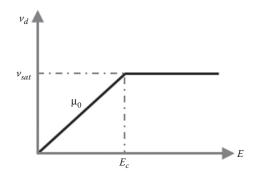

|     |       |         | 2.2.5.4   | Velocity Saturation                    | 35        |

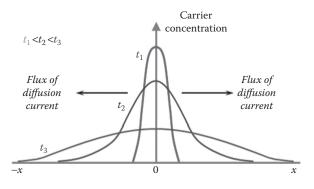

|    |            |        | 2.2.5.5    | Diffusion of Carriers                                                  | 36 |

|----|------------|--------|------------|------------------------------------------------------------------------|----|

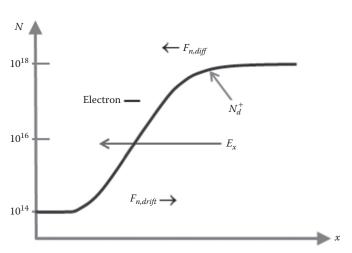

|    |            |        | 2.2.5.6    | Nonuniformly Doped Semiconductors                                      |    |

|    |            |        |            | and Built-In Electric Field                                            | 38 |

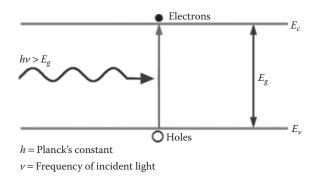

|    |            | 2.2.6  | Generat    | tion-Recombination                                                     | 39 |

|    |            |        | 2.2.6.1    | Injection Level                                                        | 40 |

|    |            |        | 2.2.6.2    | Recombination Processes                                                |    |

|    |            | 2.2.7  | Basic Se   | emiconductor Equations                                                 | 44 |

|    |            |        | 2.2.7.1    | Poisson's Equation                                                     |    |

|    |            |        | 2.2.7.2    |                                                                        |    |

|    |            |        |            | of Electrostatic Potential                                             | 46 |

|    |            |        | 2.2.7.3    | Quasi-Fermi Level                                                      |    |

|    |            |        | 2.2.7.4    | -                                                                      |    |

|    |            |        | 2.2.7.5    |                                                                        |    |

|    | 2.3        | Theory |            | pe and <i>p</i> -Type Semiconductors in Contact                        |    |

|    |            | 2.3.1  |            | eatures of <i>pn</i> -Junctions                                        |    |

|    |            | 2.3.2  |            | Potential                                                              |    |

|    |            | 2.3.3  |            | nctions                                                                |    |

|    |            | 2.0.0  | 2.3.3.1    | Junction Potential and Electric Field                                  |    |

|    |            | 2.3.4  |            | tions under External Bias                                              |    |

|    |            | 2.0.1  | 2.3.4.1    | One-Sided Step Junctions                                               |    |

|    |            | 2.3.5  |            | tion Equations                                                         |    |

|    |            | 2.0.0  | 2.3.5.1    | Relationship between Minority Carrier                                  | 00 |

|    |            |        | 2.3.3.1    | Density and Junction Voltage                                           | 61 |

|    |            | 2.3.6  | nn Iuno    | tions <i>I–V</i> Characteristics                                       |    |

|    |            | 2.3.0  | 2.3.6.1    | Temperature Dependence of <i>pn</i> -Junction                          | 05 |

|    |            |        | 2.3.0.1    |                                                                        | 67 |

|    |            |        | 2.3.6.2    | Leakage Current                                                        |    |

|    |            |        | 2.3.6.2    | Limitations of <i>pn</i> -Junction Current Equation<br>Bulk Resistance |    |

|    |            |        |            |                                                                        |    |

|    |            | 227    | 2.3.6.4    | ,                                                                      |    |

|    |            | 2.3.7  |            | tion Dynamic Behavior                                                  |    |

|    |            |        | 2.3.7.1    | Junction Capacitance                                                   | 73 |

|    |            |        | 2.3.7.2    |                                                                        | 76 |

|    |            | 000    | 2.3.7.3    | Small Signal Conductance                                               | 77 |

|    | <b>a</b> 4 | 2.3.8  |            | Equivalent Circuit for Circuit CAD                                     |    |

|    | 2.4        |        |            |                                                                        |    |

|    | Exerc      | cises  |            |                                                                        | 79 |

| ~  |            | 10.1   | <b>·</b> · |                                                                        | 00 |

| 3. |            |        |            | onductor System                                                        |    |

|    | 3.1        |        |            |                                                                        |    |

|    | 3.2        |        | ·          | at Equilibrium                                                         |    |

|    |            | 3.2.1  |            | unction                                                                |    |

|    |            | 3.2.2  |            | Charges                                                                |    |

|    |            |        | 3.2.2.1    | Interface-Trapped Charge                                               |    |

|    |            |        | 3.2.2.2    | Fixed-Oxide Charge                                                     | 90 |

|    |       |        | 3.2.2.3    | Oxide-Trapped Charge                     | 91                   |

|----|-------|--------|------------|------------------------------------------|----------------------|

|    |       |        | 3.2.2.4    | Mobile Ionic Charge                      |                      |

|    |       | 3.2.3  | Flat Ban   | d Voltage                                |                      |

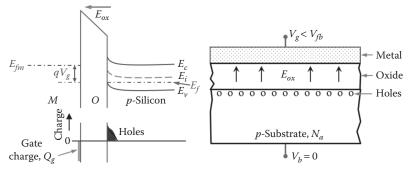

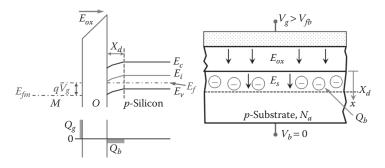

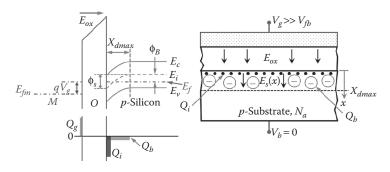

|    |       | 3.2.4  | Effect of  | Band Bending on the Semiconductor Sur    | face <mark>93</mark> |

|    | 3.3   | MOS C  |            | under Applied Bias                       |                      |

|    |       | 3.3.1  |            | llation                                  |                      |

|    |       | 3.3.2  |            | on                                       |                      |

|    |       | 3.3.3  | Inversio   | n                                        | 97                   |

|    | 3.4   | MOS C  | Capacitor  | Theory                                   | 99                   |

|    |       | 3.4.1  | Formula    | ition of Poisson's Equation in Terms     |                      |

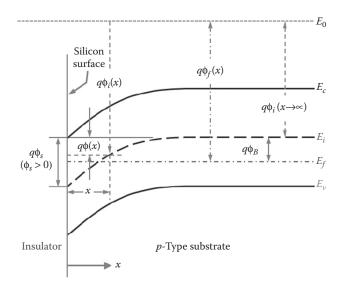

|    |       |        |            | Bending Potential.                       | 100                  |

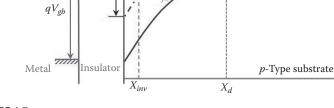

|    |       | 3.4.2  | Electros   | tatic Potentials and Charge Distribution | 103                  |

|    |       |        | 3.4.2.1    | MOS Capacitor at Depletion: Depletion    |                      |

|    |       |        |            | Approximation                            | 105                  |

|    |       |        | 3.4.2.2    | MOS Capacitor at Inversion               | 107                  |

|    | 3.5   | Capaci | tance of I | MOS Structure                            | 114                  |

|    |       | 3.5.1  | Low Fre    | quency C–V Characteristics               | 115                  |

|    |       |        | 3.5.1.1    | Accumulation                             | 116                  |

|    |       |        | 3.5.1.2    | Flat Band                                | 116                  |

|    |       |        | 3.5.1.3    | Depletion                                | 117                  |

|    |       |        | 3.5.1.4    | Inversion                                | 118                  |

|    |       | 3.5.2  | Interme    | diate and High Frequency $C-V$           |                      |

|    |       |        | Charact    | eristics                                 | 119                  |

|    |       | 3.5.3  | Deep De    | epletion <i>C–V</i> Characteristics      | 119                  |

|    |       | 3.5.4  | Deviatio   | n from Ideal C–V Curves                  |                      |

|    |       | 3.5.5  | Polysilic  | on Depletion Effect on <i>C–V</i> Curves | 121                  |

|    | 3.6   | Summ   | ary        | *                                        |                      |

|    | Exerc | ises   |            |                                          |                      |

|    |       |        |            |                                          |                      |

| 4. | Large | e Geom | etry MO    | SFET Compact Models                      | 131                  |

|    | 4.1   | Introd | uction     | _                                        | 131                  |

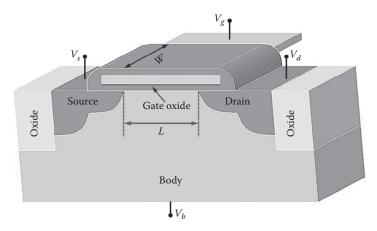

|    | 4.2   | Overvi |            | OSFET Devices                            |                      |

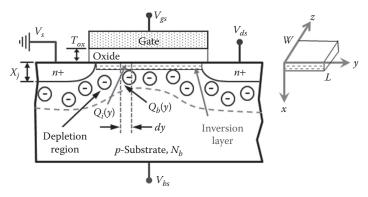

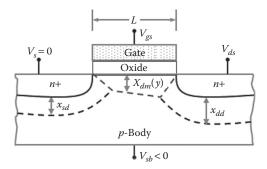

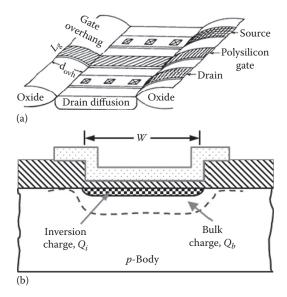

|    |       | 4.2.1  | Basic Fe   | atures of MOSFET Devices                 |                      |

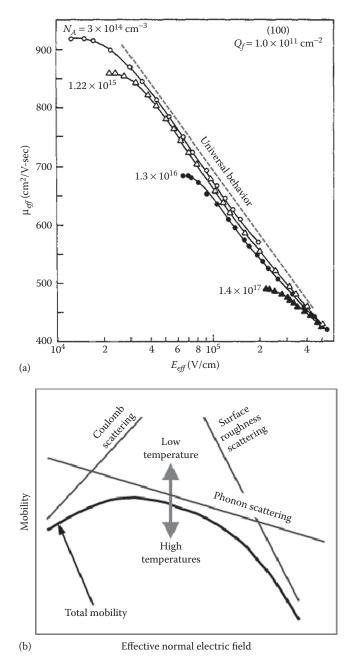

|    |       | 4.2.2  | MOSFE      | Г Device Operation                       |                      |

|    | 4.3   |        |            | hold Voltage Model                       |                      |

|    | 4.4   | MOSF   | ET Drain   | Current Model                            |                      |

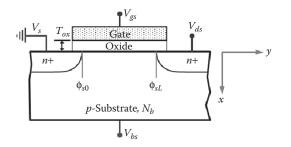

|    |       | 4.4.1  | Drain C    | urrent Formulation                       |                      |

|    |       | 4.4.2  | Pao-Sah    | Model                                    | 144                  |

|    |       | 4.4.3  | Charge-    | Sheet Model                              | 146                  |

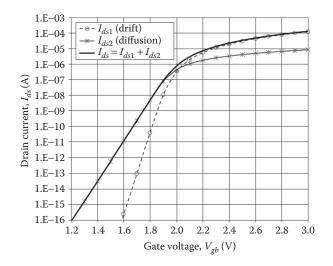

|    |       |        | 4.4.3.1    | Drift Component of Drain Current         |                      |

|    |       |        | 4.4.3.2    | Diffusion Component of Drain Current     | 148                  |

|    |       | 4.4.4  | Regiona    | l Drain Current Model                    | 150                  |

|    |       |        | 4.4.4.1    | Core Model                               | 152                  |

|    |       |        | 4.4.4.2    | Bulk-Charge Model                        | 160                  |

|    |       |        |            |                                          |                      |

|    |       |         | 4.4.4.3   | Square Root Approximation of Bulk-Charge<br>Model |      |

|----|-------|---------|-----------|---------------------------------------------------|------|

|    |       |         | 4 4 4 4   |                                                   |      |

|    |       |         | 4.4.4.4   |                                                   | 163  |

|    |       |         | 4.4.4.5   | Limitations of Regional Drain Current<br>Model    | 1(0  |

|    | 4 E   | Course  |           | Model                                             |      |

|    | 4.5   |         |           |                                                   |      |

|    | Exerc | ises    |           |                                                   | 1/ 1 |

| 5. | Com   | pact Mo | odels for | Small Geometry MOSFETs                            | 175  |

|    | 5.1   | Introd  | uction    | -                                                 | 175  |

|    | 5.2   | Thresh  | nold Volt | age Model                                         | 175  |

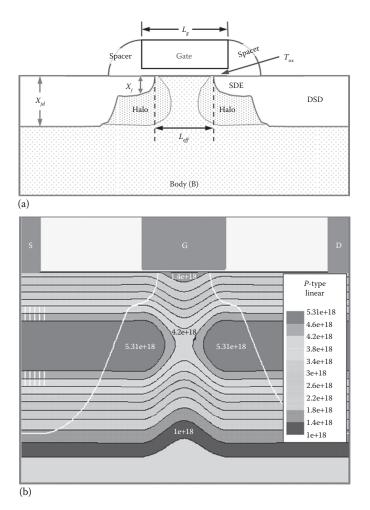

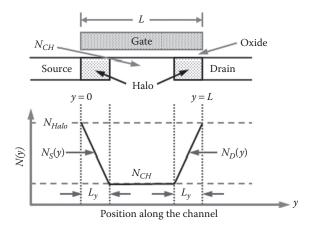

|    |       | 5.2.1   | Effect o  | f Nonuniform Channel Doping on Threshold          |      |

|    |       |         | Voltage   |                                                   | 176  |

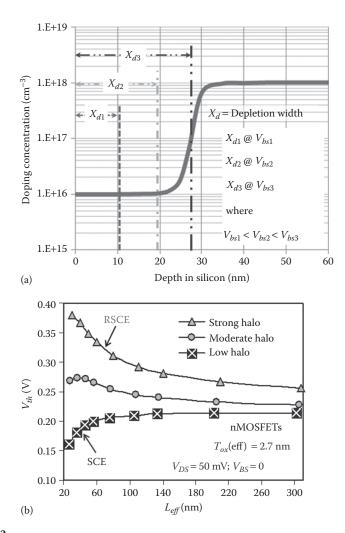

|    |       |         | 5.2.1.1   | Threshold Voltage Modeling for                    |      |

|    |       |         |           | Nonuniform Vertical Channel Doping                |      |

|    |       |         |           | Profile                                           | 177  |

|    |       |         | 5.2.1.2   | Threshold Voltage Modeling for                    |      |

|    |       |         |           | Nonuniform Lateral Channel Doping                 |      |

|    |       |         |           | Profile                                           | 180  |

|    |       | 5.2.2   |           | Geometry Effect on Threshold Voltage Model        | 183  |

|    |       |         | 5.2.2.1   |                                                   |      |

|    |       |         |           | MOSFET Devices                                    | 183  |

|    |       |         | 5.2.2.2   | Threshold Voltage Modeling for Narrow             |      |

|    |       |         |           | Channel MOSFET Devices                            | 186  |

|    | 5.3   |         | Current   | Model                                             | 190  |

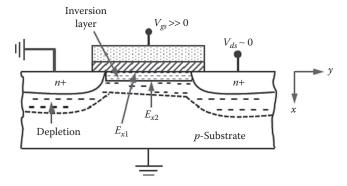

|    |       | 5.3.1   |           | Mobility Model                                    |      |

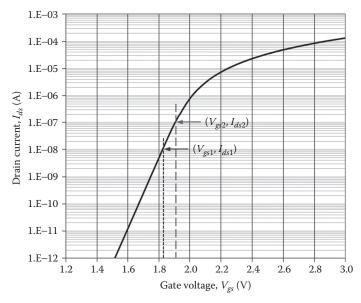

|    |       | 5.3.2   |           | eshold Region Drain Current Model                 |      |

|    |       | 5.3.3   | Linear l  | Region Drain Current Model                        | 197  |

|    |       | 5.3.4   | Saturati  | ion Region Drain Current Model                    | 200  |

|    |       | 5.3.5   | Bulk-Cl   | narge Effect                                      | 201  |

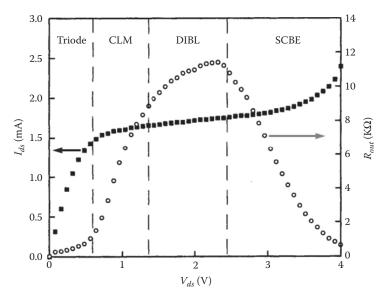

|    |       | 5.3.6   | Output    | Resistance                                        | 202  |

|    |       | 5.3.7   |           | Drain Current Equation                            |      |

|    |       | 5.3.8   | S/D Par   | casitic Series Resistance                         | 205  |

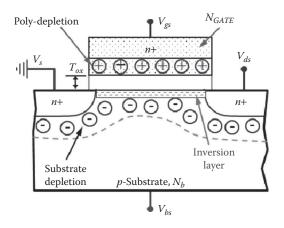

|    |       | 5.3.9   | Polysili  | con Gate Depletion                                | 205  |

|    |       | 5.3.10  | Temper    | ature Dependence                                  | 208  |

|    | 5.4   | Substr  | ate Curre | ent Model                                         | 210  |

|    |       | 5.4.1   | Gate-In   | duced Drain Leakage Body Current Model            | 218  |

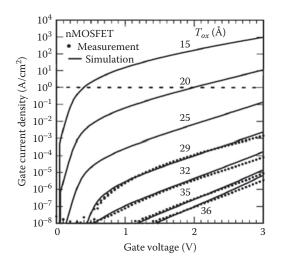

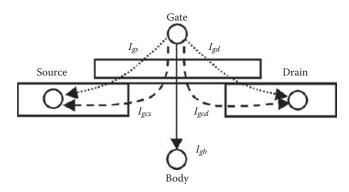

|    |       | 5.4.2   | Gate Cu   | ırrent Model                                      | 219  |

|    | 5.5   | Summ    | ary       |                                                   | 221  |

|    | Exerc | ises    |           |                                                   | 221  |

| _  |       |         | •.        | N                                                 |      |

| 6. |       |         |           | ce Models                                         |      |

|    | 6.1   |         |           |                                                   |      |

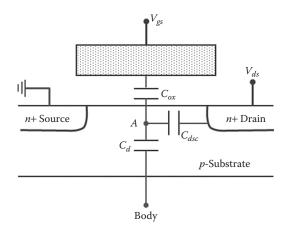

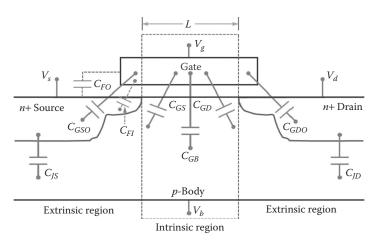

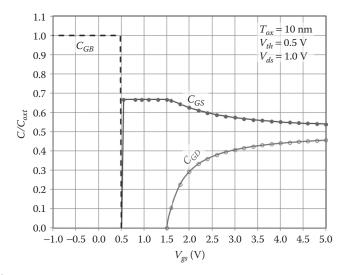

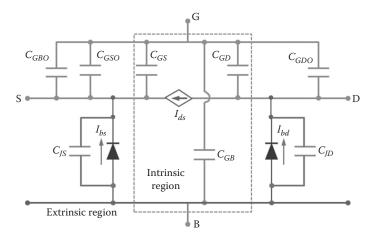

|    | 6.2   | Basic N | MOSFET    | Capacitance Model                                 | 226  |

|    |       | 6.2.1  | Intrinsic Charges   | and Capacitances           | 227               |

|----|-------|--------|---------------------|----------------------------|-------------------|

|    |       | 6.2.2  |                     | -                          |                   |

|    |       |        |                     | version                    |                   |

|    |       |        |                     | version                    |                   |

|    |       | 6.2.3  | Limitations of Me   | ver Model                  | 236               |

|    | 6.3   | Charg  | e-Based Capacitan   | e Model                    |                   |

|    |       | 6.3.1  |                     | arge Model                 |                   |

|    |       |        |                     | version                    |                   |

|    |       |        | 6.3.1.2 Weak Inv    | version                    | 244               |

|    |       |        | 6.3.1.3 Accumu      | ation                      | 246               |

|    |       | 6.3.2  | Long Channel Ca     | pacitance Model            | 246               |

|    |       | 6.3.3  | Short Channel Ch    | arge Model                 | 248               |

|    |       | 6.3.4  | Short Channel Ca    | pacitance Model            |                   |

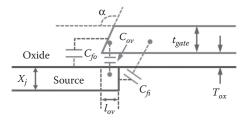

|    | 6.4   | Gate C | verlap Capacitance  | e Model                    | 251               |

|    | 6.5   | Limita | tions of the Quasis | tatic Model                | 254               |

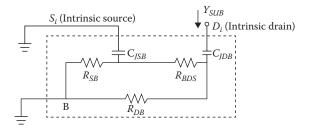

|    | 6.6   | S/D pr | -Junction Capacita  | nce Model                  |                   |

|    |       | 6.6.1  | Source-Body pn-Ju   | unction Diode              |                   |

|    |       | 6.6.2  | Drain-Body Junct    | ion Diode                  |                   |

|    | 6.7   | Summ   | ary                 |                            | 258               |

|    | Exerc | ises   |                     |                            | 259               |

|    |       |        |                     |                            |                   |

| 7. | Com   | pact M | OSFET Models for    | RF Applications            | <mark>26</mark> 1 |

|    | 7.1   |        |                     |                            |                   |

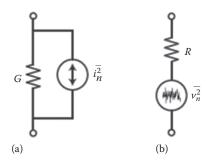

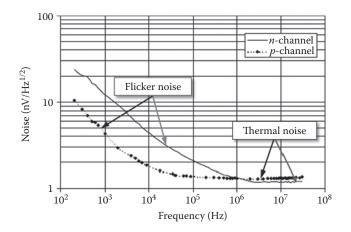

|    | 7.2   |        | ET Noise Models     |                            | 261               |

|    |       | 7.2.1  | Fundamental Sou     | rces of Noise              |                   |

|    |       | 7.2.2  |                     |                            |                   |

|    |       |        |                     | Mechanism of Thermal Noise |                   |

|    |       |        |                     | Noise Model                |                   |

|    |       | 7.2.3  |                     |                            |                   |

|    |       |        |                     | Mechanism of Flicker Noise |                   |

|    |       |        |                     | loise Model                |                   |

|    | 7.3   |        | ffect               |                            | 274               |

|    |       | 7.3.1  |                     | fect in MOSFETs            |                   |

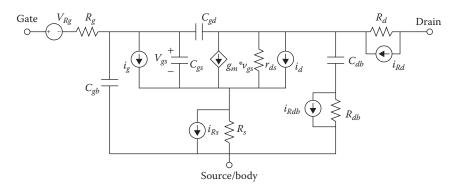

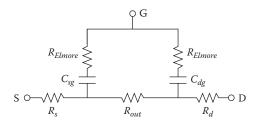

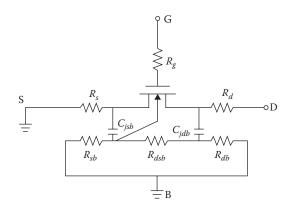

|    | 7.4   | Mode   |                     | ents for RF Applications   |                   |

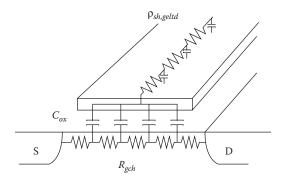

|    |       | 7.4.1  |                     | esistance                  |                   |

|    |       | 7.4.2  | Modeling Substra    | te Network                 |                   |

|    |       | 7.4.3  |                     | el for GHz Applications    |                   |

|    | 7.5   | Summ   | ary                 |                            |                   |

|    | Exerc | ises   |                     |                            |                   |

|    |       |        |                     |                            |                   |

| 8. | Mode  |        |                     | in Scaled MOSFETs          |                   |

|    | 8.1   |        |                     |                            |                   |

|    | 8.2   | Source |                     | cess Variability           |                   |

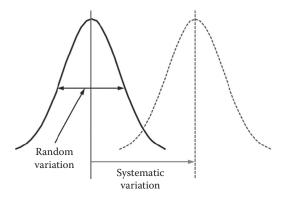

|    |       | 8.2.1  | Systematic or Glo   | bal Process Variability    |                   |

|       | 8.2.2                                                         | Randon                                        | n or Local Process Variability                         | 287 |  |

|-------|---------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------|-----|--|

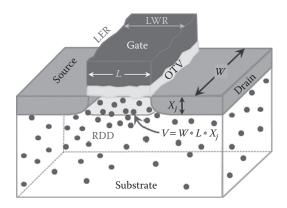

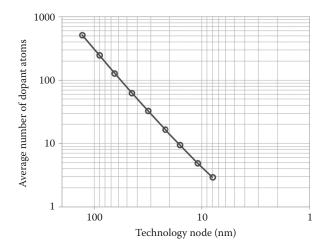

|       |                                                               | 8.2.2.1                                       |                                                        |     |  |

|       |                                                               | 8.2.2.2                                       | Line-Edge Roughness                                    |     |  |

|       |                                                               | 8.2.2.3                                       | 0 0                                                    |     |  |

|       |                                                               |                                               | Other Sources Process Variability                      |     |  |

| 8.3   | Chara                                                         |                                               | on of Parametric Variability in MOSFETs                |     |  |

|       | 8.3.1                                                         |                                               | n Variability                                          |     |  |

|       | 8.3.2                                                         |                                               | atic Variability                                       |     |  |

| 8.4   |                                                               |                                               | Process Variability Modeling for Circuit CAD.          |     |  |

|       | 8.4.1                                                         |                                               | Case Fixed Corner Models                               |     |  |

|       | 8.4.2                                                         |                                               | al Corner Models                                       |     |  |

|       | 8.4.3                                                         |                                               | Parameters-Based Compact Variability                   |     |  |

|       |                                                               |                                               | ng                                                     | 296 |  |

| 8.5   | Statist                                                       |                                               | pact Modeling                                          |     |  |

|       | 8.5.1                                                         |                                               | ination of Process Variability-Sensitive               |     |  |

|       | 0.011                                                         |                                               | T Device Parameters                                    | 298 |  |

|       |                                                               | 8.5.1.1                                       |                                                        |     |  |

|       |                                                               | 0.01111                                       | Variability-Sensitive Device Parameters                | 298 |  |

|       |                                                               | 8.5.1.2                                       | Selection of Global Process                            |     |  |

|       |                                                               | 0.0.1.2                                       | Variability-Sensitive Device Parameters                | 299 |  |

|       | 8.5.2                                                         | Mapping Process Variability-Sensitive         |                                                        |     |  |

|       | 0.0.2                                                         | Device Parameters to Compact Model Parameters |                                                        |     |  |

|       |                                                               | 8.5.2.1                                       | Mapping Local Process Variability-Sensitive            |     |  |

|       |                                                               | 0.3.2.1                                       | Device Parameters to Compact Model                     |     |  |

|       |                                                               |                                               | Parameters                                             | 301 |  |

|       |                                                               | 8.5.2.2                                       | Mapping Global Process                                 |     |  |

|       |                                                               | 0.J.Z.Z                                       | Variability-Sensitive Device Parameters                |     |  |

|       |                                                               |                                               |                                                        | 202 |  |

|       | 8.5.3                                                         | Determ                                        | to Compact Model Parameters<br>ination of Variance for |     |  |

|       | 0.3.3                                                         |                                               |                                                        |     |  |

|       |                                                               |                                               | Variability-Sensitive Compact Model                    | 202 |  |

|       |                                                               |                                               | ters                                                   | 303 |  |

|       |                                                               | 8.5.3.1                                       | Variance of Local Process                              |     |  |

|       |                                                               |                                               | Variability-Sensitive Compact Model                    | 202 |  |

|       |                                                               |                                               | Parameters                                             | 303 |  |

|       |                                                               | 8.5.3.2                                       |                                                        |     |  |

|       |                                                               |                                               | Variability-Sensitive Compact Model                    |     |  |

|       |                                                               |                                               | Parameters                                             | 304 |  |

|       | 8.5.4                                                         |                                               | ation of Compact Model for Process                     |     |  |

|       |                                                               |                                               | lity-Aware Circuit Design                              |     |  |

|       | 8.5.5                                                         |                                               | ion Results and Discussions                            | 308 |  |

| 8.6   | Mitigation of the Risk of Process Variability in VLSI Circuit |                                               |                                                        |     |  |

|       | Performance                                                   |                                               |                                                        |     |  |

| 8.7   |                                                               | 5                                             |                                                        |     |  |

| Exerc | cises                                                         |                                               |                                                        | 311 |  |

| 9.  | Compa                                                                  | act Mod                 | els for Ult | rathin Body FETs                    |     |  |

|-----|------------------------------------------------------------------------|-------------------------|-------------|-------------------------------------|-----|--|

|     | 9.1                                                                    | Introdu                 | ction       | -                                   | 313 |  |

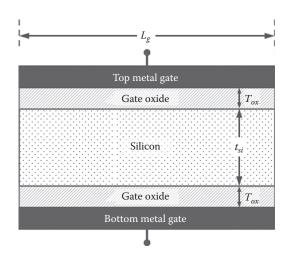

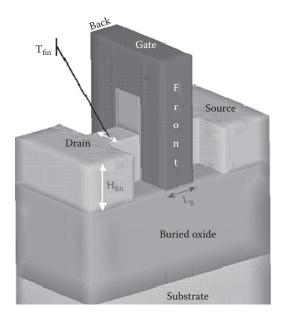

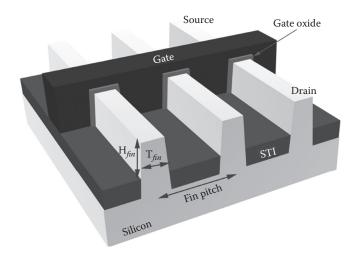

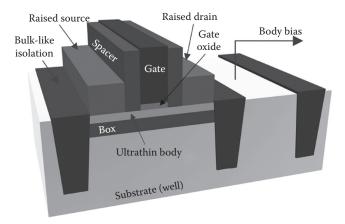

|     | 9.2                                                                    | Multiga                 | ate Device  | Structures                          | 314 |  |

|     |                                                                        | 9.2.1                   | Bulk-Mu     | ltigate Device Structure            | 314 |  |

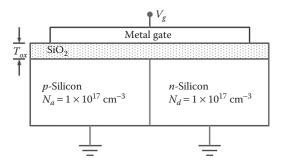

|     |                                                                        | 9.2.2                   | UTB-SOI     | Device Structure                    |     |  |

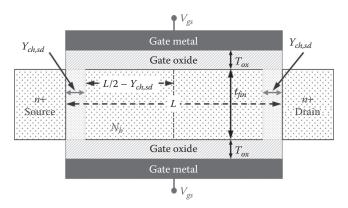

|     | 9.3                                                                    | Commo                   | on Multipl  | e-Gate FinFET Model                 |     |  |

|     |                                                                        | 9.3.1                   | Core Mo     | del: Poisson-Carrier Transport      |     |  |

|     |                                                                        |                         | 9.3.1.1     | Electrostatics                      |     |  |

|     |                                                                        |                         | 9.3.1.2     | Drain Current Model                 |     |  |

|     |                                                                        | 9.3.2                   |             | g Physical Effects of Real Device   |     |  |

|     |                                                                        |                         | 9.3.2.1     | Short Channel Effects               |     |  |

|     |                                                                        |                         | 9.3.2.2     | Quantum Mechanical Effects          |     |  |

|     |                                                                        |                         | 9.3.2.3     | Mobility Degradation                |     |  |

|     |                                                                        |                         | 9.3.2.4     | Series Resistances                  |     |  |

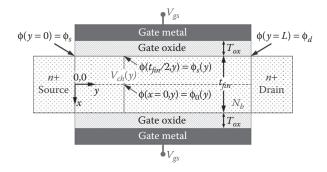

|     | 9.4                                                                    | *                       |             | tiple-Gate FET Model                |     |  |

|     |                                                                        | 9.4.1                   |             | atics                               |     |  |

|     |                                                                        | 9.4.2                   |             | ırrent Model                        |     |  |

|     | 9.5                                                                    | 5                       |             |                                     |     |  |

|     |                                                                        | 9.5.1                   |             | Multigate <i>C</i> – <i>V</i> Model |     |  |

|     | <b>.</b>                                                               | 9.5.2                   |             | lent Multigate <i>C–V</i> Model     |     |  |

|     | 9.6                                                                    |                         |             |                                     |     |  |

|     | Exercis                                                                | ses                     | •••••       |                                     |     |  |

| 10  | Dowom                                                                  | 1 CMO                   | C Transist  | or Modeles Turnel EETs              | 242 |  |

| 10. | <b>Beyond-CMOS Transistor Models: Tunnel FETs</b><br>10.1 Introduction |                         |             |                                     |     |  |

|     | 10.1                                                                   | Basic Features of TFETs |             |                                     |     |  |

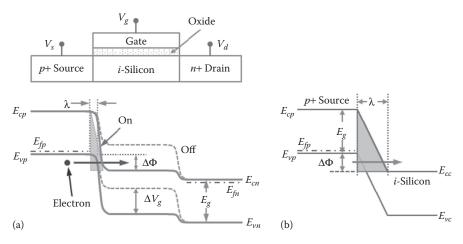

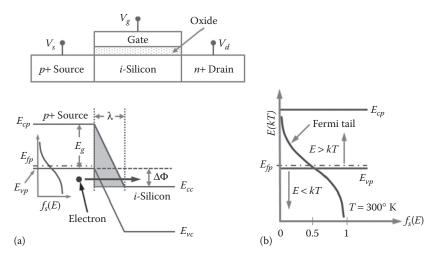

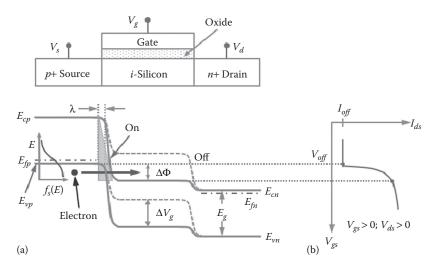

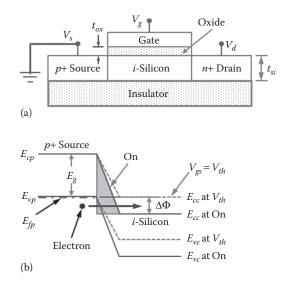

|     | 10.2                                                                   |                         |             | FET Operation                       |     |  |

|     | 10.5                                                                   | 10.3.1                  |             | and Diagram                         |     |  |

|     |                                                                        | 10.3.2                  |             | g Mechanism                         |     |  |

|     |                                                                        | 10.3.3                  |             | haracteristics                      |     |  |

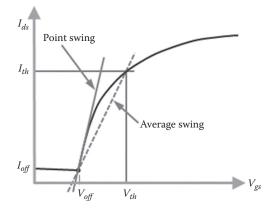

|     |                                                                        | 10.3.4                  |             | hold Swing                          |     |  |

|     | 10.4                                                                   |                         |             | siderations                         |     |  |

|     | 10.5                                                                   |                         |             | odels                               |     |  |

|     |                                                                        | 10.5.1                  |             | d Voltage Model                     |     |  |

|     |                                                                        | 10.5.2                  |             | irrent Model                        |     |  |

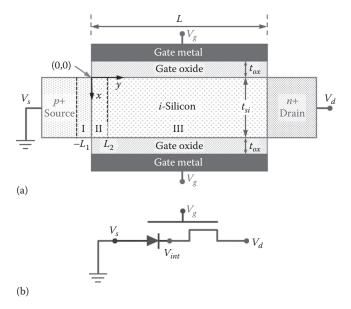

|     |                                                                        |                         | 10.5.2.1    | Ideal Drain Current Model           |     |  |

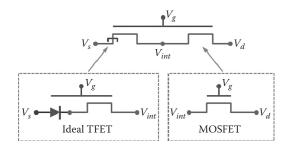

|     |                                                                        |                         | 10.5.2.2    | Modeling the Channel Transports     |     |  |

|     |                                                                        |                         |             | Using Drain MOSFET                  |     |  |

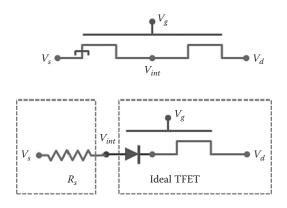

|     |                                                                        |                         | 10.5.2.3    | Modeling the Channel Transports     |     |  |

|     |                                                                        |                         |             | Using Source Resistance             |     |  |

|     | 10.6                                                                   | Summa                   | nry         |                                     |     |  |

|     |                                                                        |                         | 2           |                                     |     |  |

|     | Exercis                                                                | ses                     |             |                                     |     |  |

| 11. | Bipola        |                                                         | on Transistor Compact Models                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

|-----|---------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|     | 11.1          |                                                         | action                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

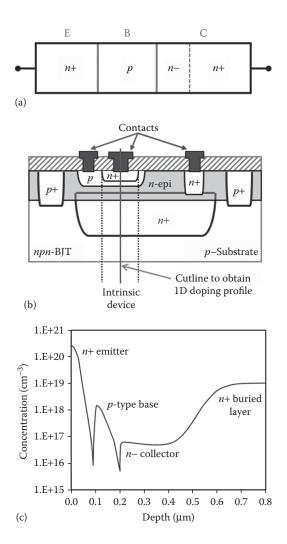

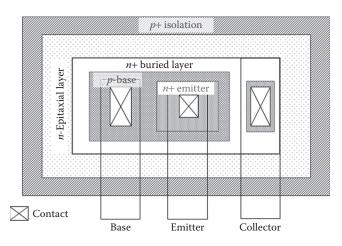

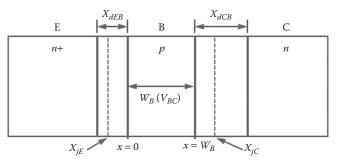

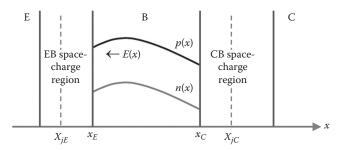

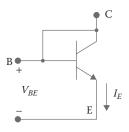

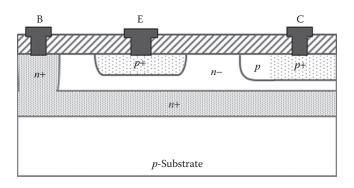

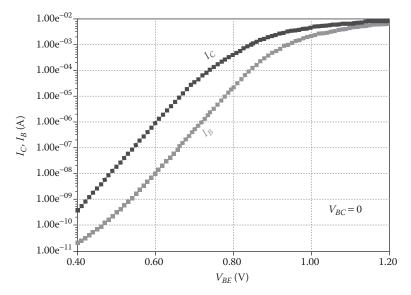

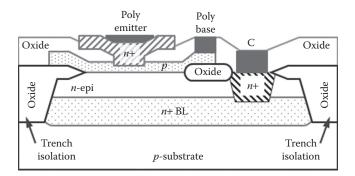

|     | 11.2          | Basic F                                                 | eatures of BJTs                                                                                                                                                                                                                                                                                                                                                                             | 372                                                                       |

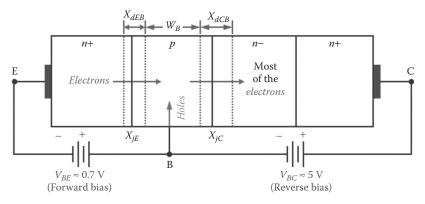

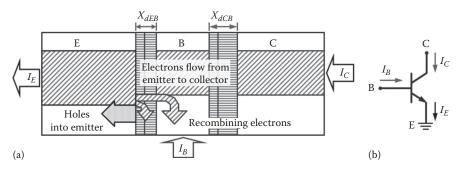

|     | 11.3          |                                                         | Operation of BJTs                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

|     | 11.4          |                                                         | of Operations of BJTs                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |

|     | 11.5          | Compa                                                   | ct BJT Model                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

|     |               | 11.5.1                                                  | Basic DC Model: EM1                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|     |               |                                                         | 11.5.1.1 Linear Hybrid-π Small Signal Model                                                                                                                                                                                                                                                                                                                                                 | 382                                                                       |

|     |               | 11.5.2                                                  |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

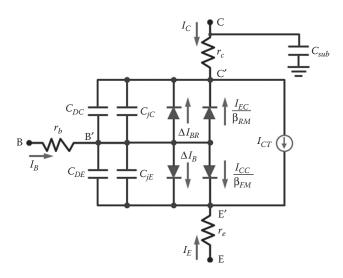

|     |               |                                                         | 11.5.2.1 Modeling Parasitic Circuit Elements                                                                                                                                                                                                                                                                                                                                                | 385                                                                       |

|     |               |                                                         | 11.5.2.2 Limitations of Basic Model                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|     |               | 11.5.3                                                  | Modeling Carrier Recombination in the Depletion                                                                                                                                                                                                                                                                                                                                             |                                                                           |

|     |               |                                                         | Regions                                                                                                                                                                                                                                                                                                                                                                                     | 394                                                                       |

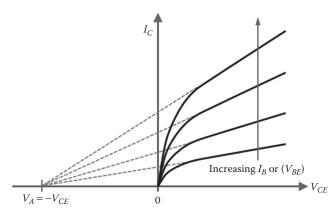

|     |               | 11.5.4                                                  | Modeling Base-Width Modulation and                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

|     |               |                                                         | High-Level Injection                                                                                                                                                                                                                                                                                                                                                                        | 395                                                                       |

|     |               |                                                         | 11.5.4.1 Components of Injected Base Charge                                                                                                                                                                                                                                                                                                                                                 | 402                                                                       |

|     |               | 11.5.5                                                  | Summary of Compact BJT Model                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

|     | 11.6          | Summa                                                   | ary                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|     | Exercia       | ses                                                     | ·                                                                                                                                                                                                                                                                                                                                                                                           | 415                                                                       |

|     |               |                                                         |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

| 12. | Comp          | act Mod                                                 | el Library for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                           | 423                                                                       |

|     | 12.1          |                                                         | action                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

|     | 12.2          | Genera                                                  | l Approach to Generate Compact Device Model                                                                                                                                                                                                                                                                                                                                                 | 423                                                                       |

|     |               | 12.2.1                                                  | Data Collection                                                                                                                                                                                                                                                                                                                                                                             | 423                                                                       |

|     |               |                                                         |                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

|     |               |                                                         | 12.2.1.1 Selection of Devices                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

|     |               |                                                         | 12.2.1.1 Selection of Devices                                                                                                                                                                                                                                                                                                                                                               | 424                                                                       |

|     |               | 12.2.2                                                  |                                                                                                                                                                                                                                                                                                                                                                                             | 424<br>426                                                                |

|     |               | 12.2.2<br>12.2.3                                        | 12.2.1.2 Selection of Device Characteristics                                                                                                                                                                                                                                                                                                                                                | 424<br>426<br>427                                                         |

|     |               |                                                         | 12.2.1.2 Selection of Device Characteristics<br>Data Fitting to Extract Compact Model Parameters<br>Generation of Parameter Files                                                                                                                                                                                                                                                           | 424<br>426<br>427<br>428                                                  |

|     |               | 12.2.3                                                  | 12.2.1.2 Selection of Device Characteristics<br>Data Fitting to Extract Compact Model Parameters<br>Generation of Parameter Files<br>Generation of Compact Model Library                                                                                                                                                                                                                    | 424<br>426<br>427<br>428<br>429                                           |

|     |               | 12.2.3                                                  | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> </ul>                                                                                                                    | 424<br>426<br>427<br>428<br>429<br>430                                    |

|     |               | 12.2.3                                                  | 12.2.1.2 Selection of Device Characteristics<br>Data Fitting to Extract Compact Model Parameters<br>Generation of Parameter Files<br>Generation of Compact Model Library                                                                                                                                                                                                                    | 424<br>426<br>427<br>428<br>429<br>430<br>433                             |

|     |               | 12.2.3                                                  | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> <li>12.2.4.2 Modeling Mismatch</li> </ul>                                                                                | 424<br>426<br>427<br>428<br>429<br>430<br>433<br>434                      |

|     | 12.3          | 12.2.3<br>12.2.4<br>12.2.5                              | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> <li>12.2.4.2 Modeling Mismatch</li> <li>12.2.4.3 Generate Model Card</li> <li>Model Validation</li> </ul>                | 424<br>426<br>427<br>428<br>429<br>430<br>433<br>434<br>436               |

|     | 12.3<br>12.4  | 12.2.3<br>12.2.4<br>12.2.5<br>Model                     | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> <li>12.2.4.2 Modeling Mismatch</li> <li>12.2.4.3 Generate Model Card</li> <li>Model Validation</li> <li>Usage</li> </ul> | 424<br>426<br>427<br>428<br>429<br>430<br>433<br>434<br>436<br>436        |

|     | 12.4          | 12.2.3<br>12.2.4<br>12.2.5<br>Model<br>Summa            | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> <li>12.2.4.2 Modeling Mismatch</li> <li>12.2.4.3 Generate Model Card</li> <li>Model Validation</li> <li>Usage</li> </ul> | 424<br>426<br>427<br>428<br>429<br>430<br>433<br>434<br>436<br>439        |

|     | 12.4          | 12.2.3<br>12.2.4<br>12.2.5<br>Model<br>Summa            | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> <li>12.2.4.2 Modeling Mismatch</li> <li>12.2.4.3 Generate Model Card</li> <li>Model Validation</li> <li>Usage</li> </ul> | 424<br>426<br>427<br>428<br>429<br>430<br>433<br>434<br>436<br>439        |

| Ref | 12.4<br>Sampl | 12.2.3<br>12.2.4<br>12.2.5<br>Model<br>Summa<br>e Model | <ul> <li>12.2.1.2 Selection of Device Characteristics</li> <li>Data Fitting to Extract Compact Model Parameters</li> <li>Generation of Parameter Files</li> <li>Generation of Compact Model Library</li> <li>12.2.4.1 Modeling Systematic Process Variability</li> <li>12.2.4.2 Modeling Mismatch</li> <li>12.2.4.3 Generate Model Card</li> <li>Model Validation</li> <li>Usage</li> </ul> | 424<br>426<br>427<br>428<br>429<br>430<br>433<br>434<br>436<br>439<br>440 |

## Preface

Silicon integrated circuits (ICs) have ushered in an unprecedented revolution in many areas of today's society, including communications, medicine, military, security, and entertainment. This dramatic impact of ICs on society is due to the continuous miniaturization of metal-oxide-semiconductor (MOS) field-effect-transistor (FET) devices toward their ultimate dimensions of approximately 5 nm, thereby providing low-cost, high-density, fast, and low-power ICs. Our ability to fabricate billions of individual components on a silicon chip of a few centimeters squared has enabled the information age. However, with increase in the device densities in ICs, the complexities of IC design have increased significantly. Designing such complex IC chips is virtually impossible without computer-aided design (CAD) tools that help predict circuit behavior prior to manufacturing. However, the accuracy of CAD for ICs depends on the accuracy of the models, referred to as "compact models," of the active and passive elements used in the circuit. These compact models for circuit CAD have been the basic requirement for the analysis and design of ICs and are playing an ever-increasing role as the mainstream MOSFETs approach their fundamental scaling limit. Therefore, for efficient IC design using nanoscale devices, a detailed understanding of compact models for circuit CAD is crucial.

A large number of research articles as well as books are available on modeling nanoscale devices. Most of the published works on compact models for IC design CAD are extended user manuals of any industry standard compact MOS model and some are a collection of articles from contributed authors. Thus, the available books do not provide adequate background knowledge of compact models for beginners in industry as well as classroom teachers. In addition, the available titles on compact models do not deal with the major issue of process variability, which severely impacts device and circuit performance in advanced technologies and requires statistical compact models. Again, though the CMOS technology continues to be the pervasive technology of ICs, bipolar-junction transistors (BJTs) are an important element of IC chips. However, most of the compact modeling books do not discuss BJTs or BJT modeling for circuit CAD. Thus, a new treatise on compact modeling is crucial to address current modeling issues and understand new models for emerging devices.

With over 25 years in the field of semiconductor processes, device, and circuit CAD in industry and over 10 years in the teaching of compact modeling courses in academia, I felt the need for a comprehensive book that presents MOSFET, BJT, and statistical models and methodologies for IC design CAD. This book fulfills that need. Starting from basic semiconductor physics, this book presents advanced industry standard models for BJTs, MOSFETs, FinFETs, and TFETs along with statistical MOS models. Thus, this book is useful to beginners as well as experts in the field of microelectronics devices and design engineering.

This book is intended for the senior undergraduate and graduate courses in electrical and electronics engineering programs and researchers and practitioners working in the area of electron devices. However, the presentation of the materials is such that even an undergraduate student not familiar with semiconductor physics can understand the basic concepts of compact modeling. A limited number of exercise problems are included at the end of each chapter, a feature that would help use of this book as a text for teaching at the senior undergraduate and graduate level courses in academia.

Chapter 1 provides an overview of compact transistor and interconnection models, a brief history of compact MOSFET models, and the motivation for compact models for very-large-scale-integrated (VLSI) circuit CAD. Chapter 2 reviews of basic semiconductor physics and *pn*-junction operations.

Chapter 3 presents MOS capacitor systems and the basic theory of two terminal devices. This chapter provides the background for developing four terminal MOSFET compact models for VLSI circuit CAD.

Chapter 4 describes the basic theory of long channel MOSFETs, including the Pao-Sah model, the charge-sheet model, and earlier generations of compact models. Chapter 5 provides detailed mathematical steps to derive the industry standard Berkeley Short Channel Insulated-Gate MOSFET version 4 (BSIM4) compact model. Chapter 5 also presents the parasitic models associated with MOSFET devices, including source/drain diode compact models. Chapter 6 presents the dynamic behavior and compact MOSFET intrinsic capacitance model. Chapter 7 describes the compact MOSFET modeling techniques for noise and radio-frequency circuit CAD.

**Chapter 8** is dedicated to compact models for process variability analysis. This chapter describes the sources of variability, circuit model for process variability, and formulation of statistical models for variability-aware VLSI circuit design. This chapter also presents the techniques for mitigating the risk of process variability in advanced nanoscale VLSI circuits by novel device and process architectures.

Chapter 9 describes the basic theory and compact model for multi-gate transistors FinFETs and UTB-SOI MOSFETs, along with model parameter extraction procedures. Chapter 10 introduces compact models beyond CMOS devices including TFET.

Chapter 11 presents BJT compact models. Similar to Chapters 4 and 5, in Chapter 11, the industry standard BJT models have been derived from basic semiconductor theory and first generation models for easy understanding by beginners while retaining the rigor for the experts in the field.

Chapter 12 includes examples of compact model libraries for industry standard circuit simulation tools, calling the model in the circuit simulation

net list (input file), and circuit simulation techniques to use the generated models.

An extensive set of references is provided at the end of this book to help the readers identify the evolution and development of compact models for VLSI circuit design and analysis.

> Samar K. Saha Santa Clara University, California

### Author

Samar K. Saha received his PhD in physics from Gauhati University, Guwahati, India, and an MS degree in engineering management from Stanford University, Stanford, California. Currently, he is an adjunct professor in the electrical engineering department at Santa Clara University, Santa Clara, California, and a technical advisor at Ultrasolar Technology, Santa Clara, California. Since 1984, he has worked at various positions for National Semiconductor, LSI Logic, Texas Instruments, Philips Semiconductors, Silicon Storage Technology, Synopsys, DSM Solutions, Silterra USA, and SuVolta. He has also worked as a faculty member in the electrical engineering departments at Southern Illinois University at Carbondale, Illinois; Auburn University, Auburn, Alabama; the University of Nevada at Las Vegas, Nevada; and the University of Colorado at Colorado Springs, Colorado. He has authored more than 100 research papers, 1 book chapter on technology CAD (TCAD), and holds 10 U.S. patents. His research interests include nanoscale device and process architecture, TCAD, compact modeling, devices for renewable energy, and TCAD and R&D management.

Dr. Saha is the 2016–2017 president of the IEEE Electron Devices Society (EDS). He is a fellow of the Institution of Engineering and Technology, London, UK, and a distinguished lecturer of IEEE EDS. He has served as the vice president of EDS Publications; an elected member of the EDS Board of Governors; editor-in-chief of IEEE *QuestEDS*; chair of EDS George Smith and Paul Rappaport awards; editor of the Region-5&6 *EDS Newsletter*, chair of the EDS Compact Modeling Technical Committee, chair of the EDS North America West Subcommittee for Regions/Chapters; a member of the IEEE Conference Publications Committee; a member of the IEEE TAB Periodicals Committee; and the treasurer, vice chair, and chair of the Santa Clara Valley EDS chapter.

Dr. Saha has served as the head guest editor for the *IEEE Transactions on Electron Devices* (T-ED) special issues on *advanced compact models and 45-nm modeling challenges* and *compact interconnect models for giga scale integration,* and as a guest editor for the T-ED special issue on *advanced modeling of power devices and their applications.* He has also served as a member of the editorial board of the *World Journal of Condensed Matter Physics,* published by Scientific Research Publishing.

1

## Introduction to Compact Models

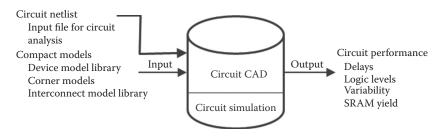

#### 1.1 Compact Models for Circuit Simulation

*Compact models* of a circuit element are simple mathematical descriptions of the behavior of that circuit element, which are used for computer-aided design (CAD) and analysis of integrated circuits (ICs). Compact models describe the device characteristics of a manufacturing technology by a set of physics-based analytical expressions with technology-dependent device model parameters that are solved by a circuit simulator for circuit analysis during IC design. *Compact modeling* refers to the art of generating compact models of an IC process technology by extracting elemental model parameters for accurate prediction of the behavior of the circuit elements of that technology in circuit simulation. In reality, the complete compact models include the modeling of each circuit element along with its parasitic components that run robustly for realistic assessment of the representative IC technology in circuit CAD [1,2].

Compact models of the circuit elements of an IC manufacturing technology have been the major part of electronic design automation (EDA) tools for circuit CAD since the invention of ICs in the year 1958 [3] and are playing an increasingly important role in the nanometer-scale system-on-chip design era. Today, compact models are the most important part of the process design kit [4,5], which is the interface between circuit designers and device technology. As the mainstream complementary metal-oxide-semiconductor (CMOS) technology is scaled down to the nanometer regime, a truly physical and predictive compact model for circuit CAD that covers geometry, bias, temperature, DC, AC, radio frequency (RF), and noise characteristics has become a major challenge for model developers and circuit designers [1]. A good compact model has to accurately capture all real-device effects and simultaneously produce them in a form suitable for maintaining high computational efficiency.

In the microelectronics industry, compact modeling includes (1) compact device models of the active devices such as bipolar junction transistors (BJTs) and metal-oxide-semiconductor field-effect transistors (MOSFETs) along with the parasitic elements of the active devices; and (2) compact interconnect models of the resistors, capacitors, and inductors of the metallization layers connecting the active devices in the ICs.

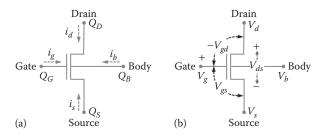

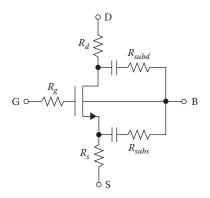

#### 1.1.1 Compact Device Models

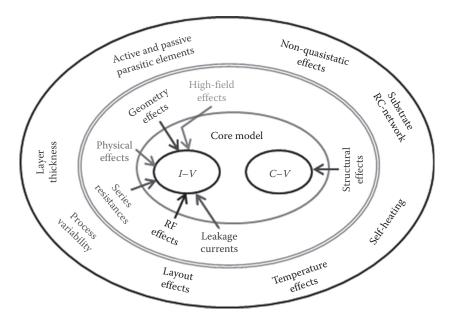

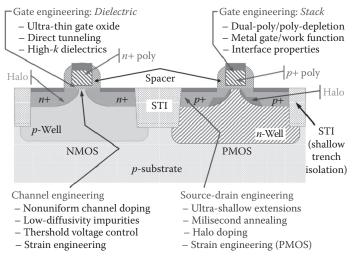

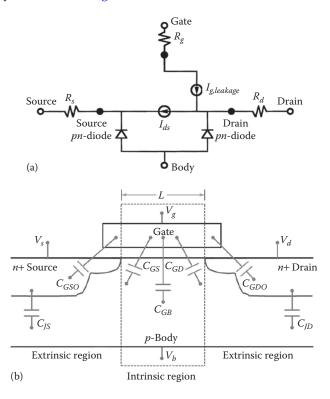

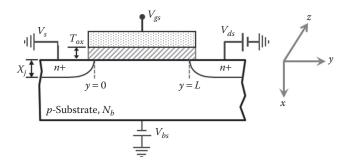

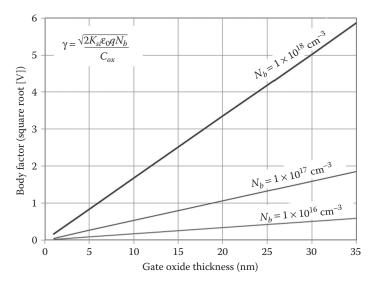

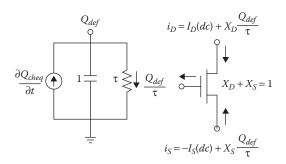

Compact device models describe the terminal behavior of a device in terms of the current-voltage (I–V), capacitance-voltage (C–V), and the carrier transport processes within the device. Figure 1.1 shows the basic features of a typical compact device model of a representative IC technology. As shown in Figure 1.1, a compact model is made of a *core model* along with the various models to account for the effects of the geometry and physical phenomena in the device. For a metal-oxide-semiconductor (MOS) transistor, the core model describes I–V and C–V behavior of an ideal large MOSFET device [4] of a target technology. The core model represents about 20% of the model code in terms of both execution time and the number of lines in the code. The rest of the model code comprises multiple models that describe the numerous real-device effects that are responsible for the accuracy of the compact

#### FIGURE 1.1

A typical composition of compact models of an IC technology: the core model includes the basic I-V and C-V behavior of a large geometry device in the inner circle; the core model is accompanied by the models for physical phenomena within the device and geometry and structural effects as shown in the middle circle; the final compact model with the geometrical and physical effects includes the external phenomena such as ambient temperature, layout effects, process variability, and NQS effects as shown in the outer circle of the model.

model. For MOSFET devices, device phenomena accompanying the core model include short-channel effects (SCEs), output conductance, quantum mechanical effects (QMEs), nonuniform doping effects, gate leakage current, band-to-band tunneling, noise, non-quasistatic (NQS) effect, intrinsic input resistance, and strain effect [4,6].

The compact model for circuit CAD is the bridge between the circuit design and processing groups and is a module of the extended technology CAD (TCAD) environment [7]. In the extended TCAD environment, the compact model plays an important role in developing next generation IC fabrication technology and assesses the manufacturability of IC fabrication processes by reverse modeling [78].

#### 1.1.2 Compact Interconnect Models

Today's very-large-scale-integrated (VLSI) circuits consist of MOSFET devices and their interconnections, referred to as interconnects. In a typical VLSI chip, the active area is about 10% whereas the physical area is occupied by interconnect and isolation regions 6-10 times the active device area [9]. For this reason, the role of the interconnect is becoming increasingly important as the feature size is scaled down to decananometer regimes and the device density is increased on the chip. As VLSI technology shrinks below 22-nm geometries with Cu/low-k interconnections, parasitics due to interconnections are becoming a limiting factor in determining circuit performance. Therefore, accurate modeling of interconnect parasitic resistance (R), capacitance (C), and inductance (L) is essential in determining various on-chip interconnectrelated issues, such as delay, cross talk, energy losses in R due to the current (I) flow or IR drop, and power dissipation. Accurate compact interconnect models are crucial for the design and optimization of advanced VLSI circuits for 22-nm CMOS technology and beyond. In addition, with the emergence of technologies such as carbon nanotubes and graphene nanoribbons, compact interconnection models that are suitable for these technologies are crucial for advanced circuit design. Currently available interconnect models, which are based on field solvers, are inadequate for accurate and meaningful analyses of today's chips, which house millions of devices. Interconnect models can accurately simulate on-chip global interconnections and speed-power optimization for advanced interconnect technologies. Modeling of these interconnect properties is thus important and must be included by the designer when checking circuit performance in circuit CAD. Though interconnect models are an essential part of optimizing VLSI circuit performance, interconnect modeling is outside the scope of this book; interested readers may refer Saha et al. [10] for recent development of interconnect models. In this treatise, compact modeling of field-effect transistors (FETs) and their parasitic components that are used in the mainstream VLSI circuit design are described.

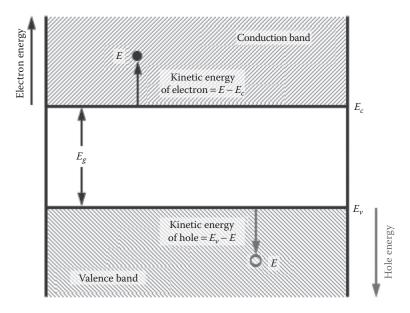

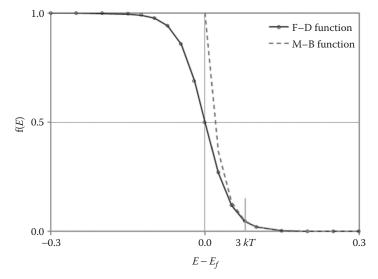

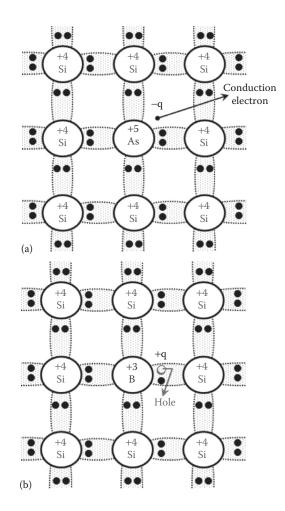

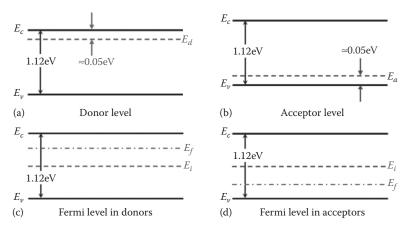

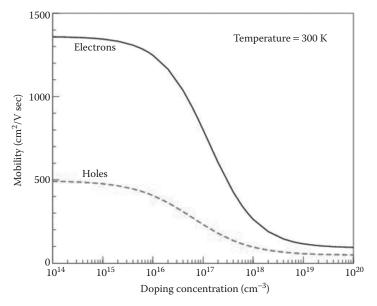

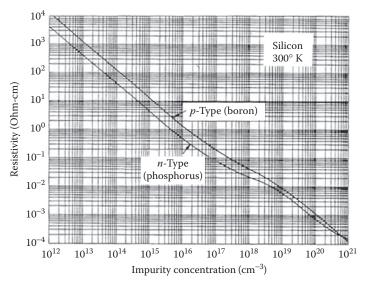

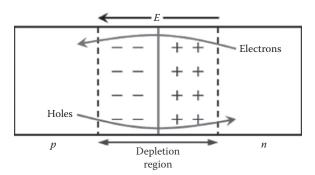

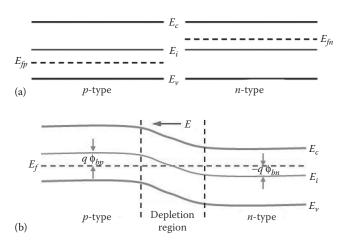

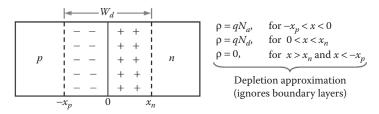

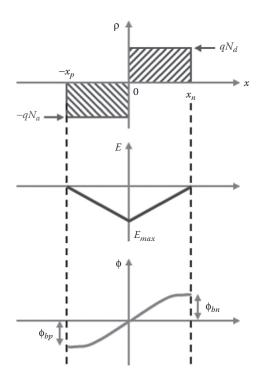

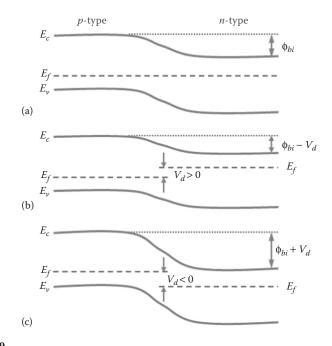

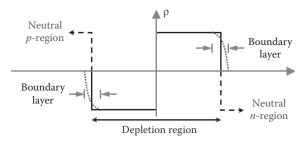

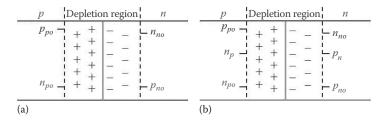

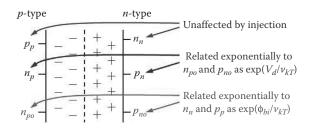

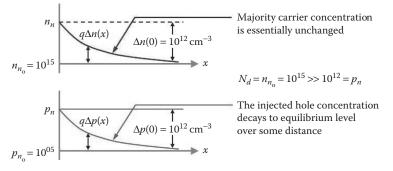

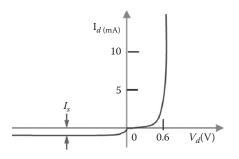

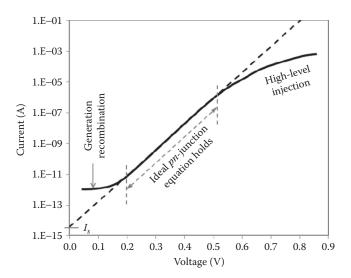

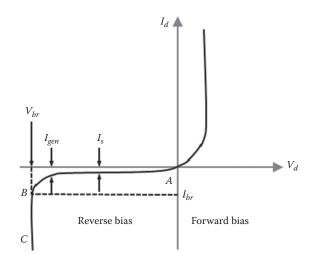

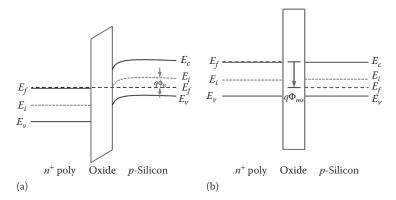

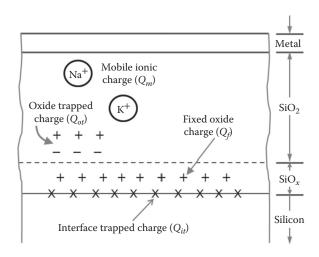

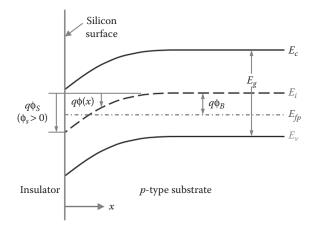

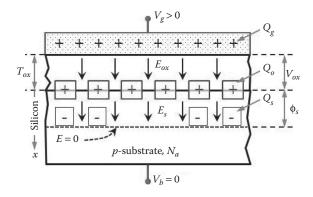

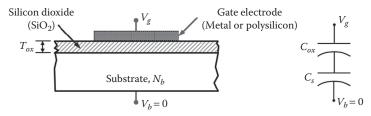

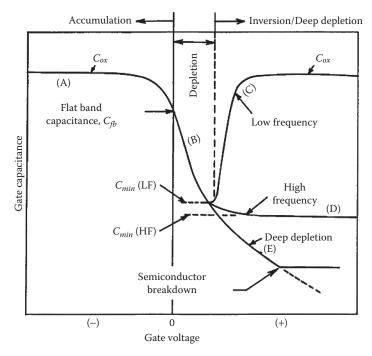

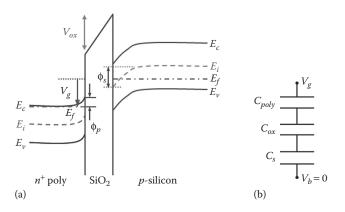

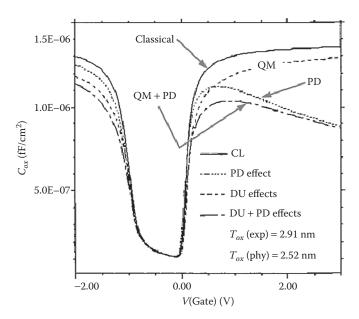

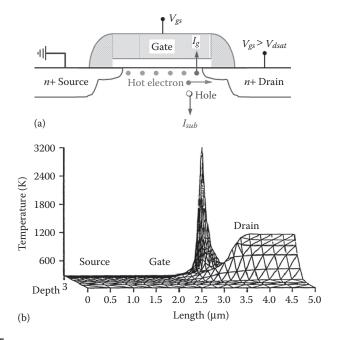

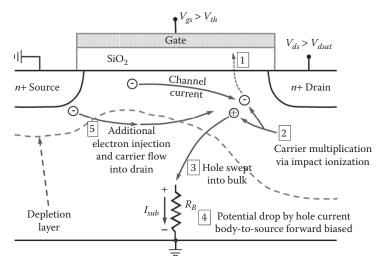

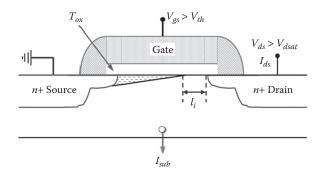

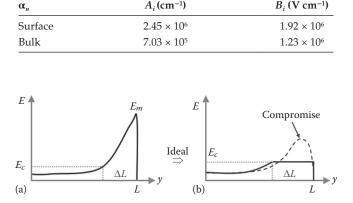

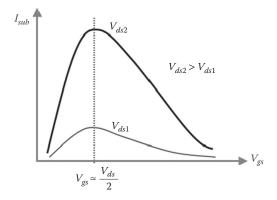

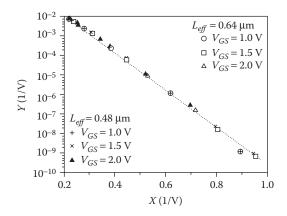

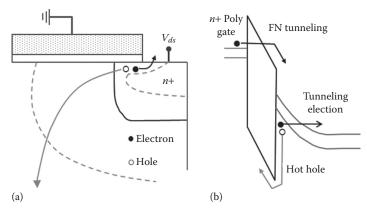

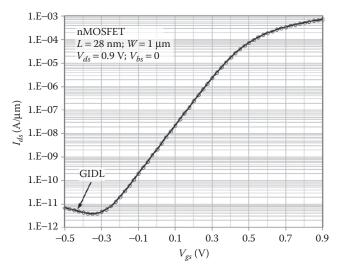

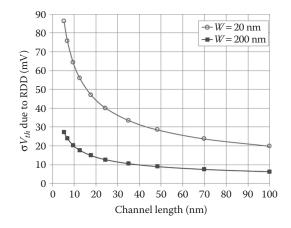

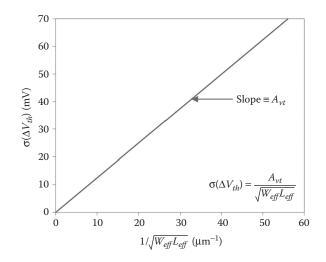

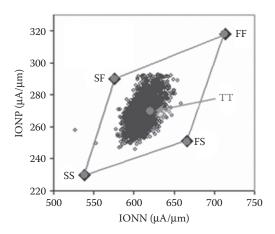

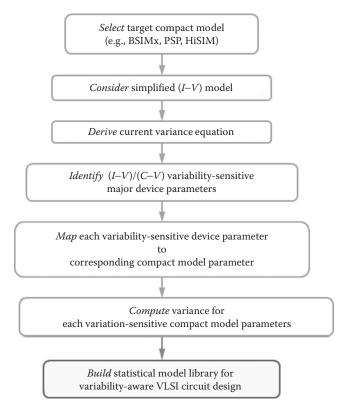

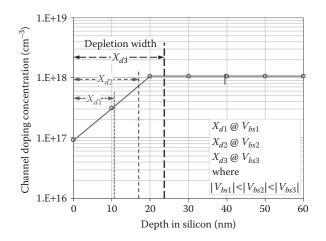

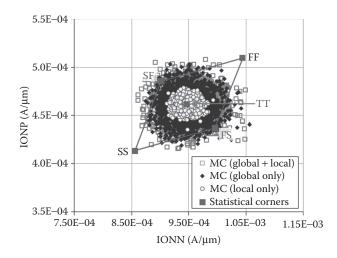

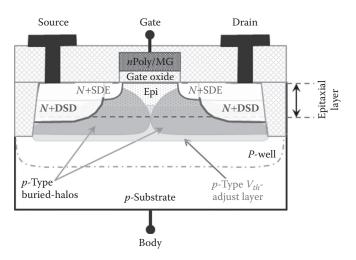

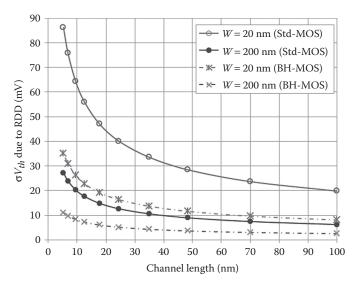

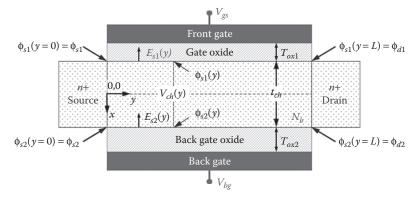

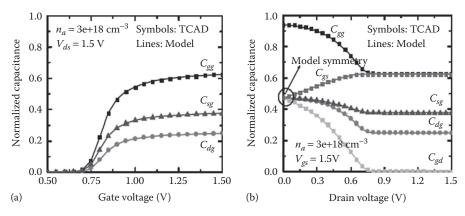

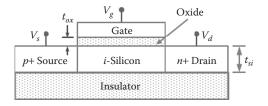

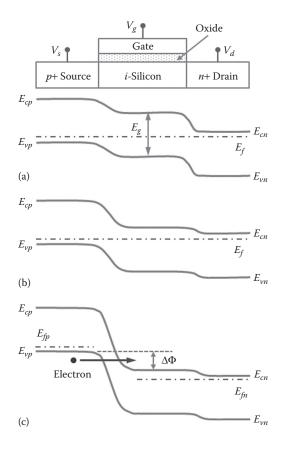

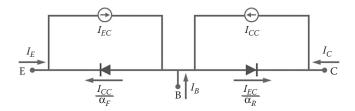

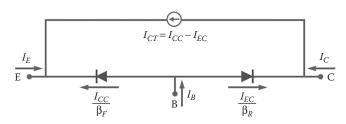

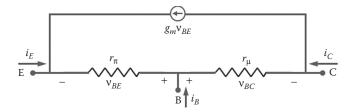

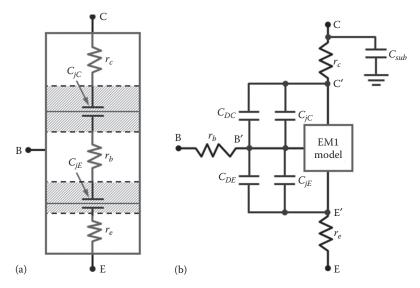

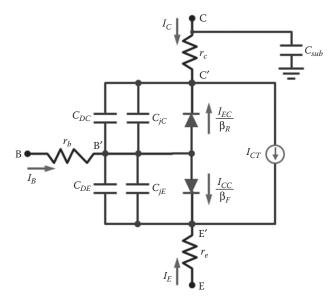

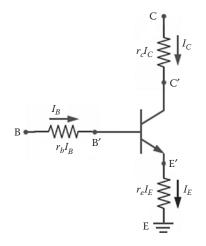

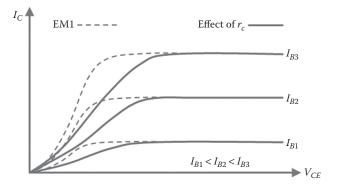

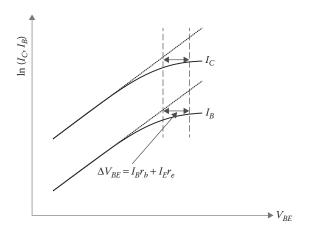

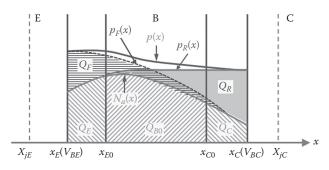

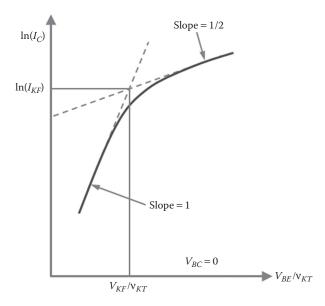

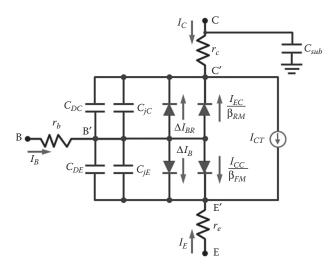

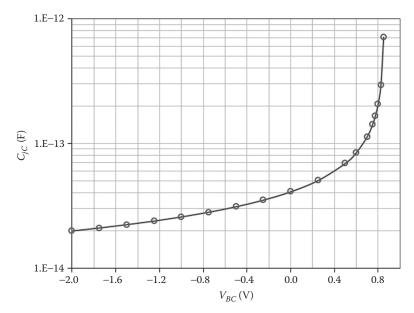

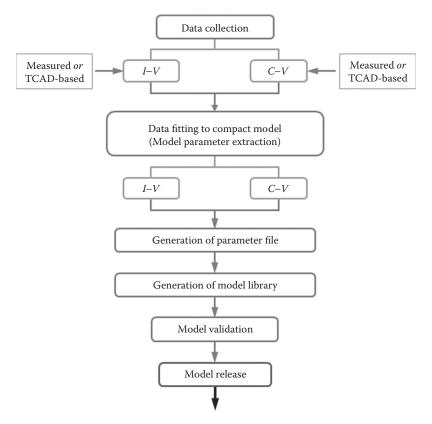

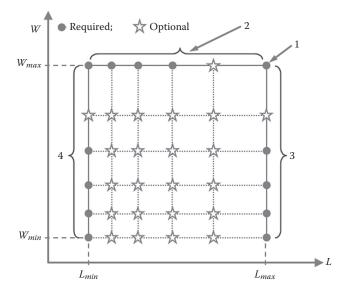

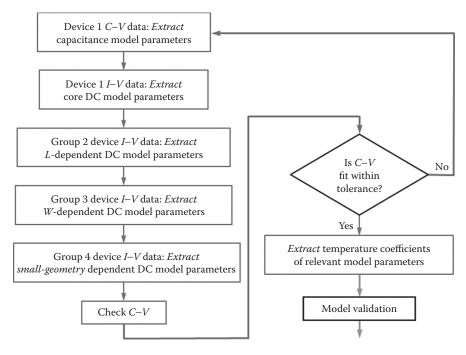

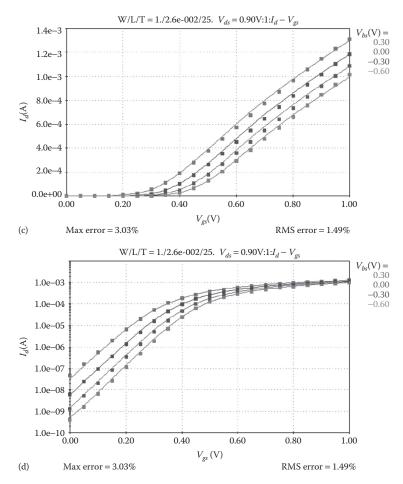

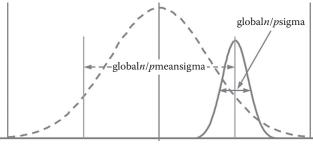

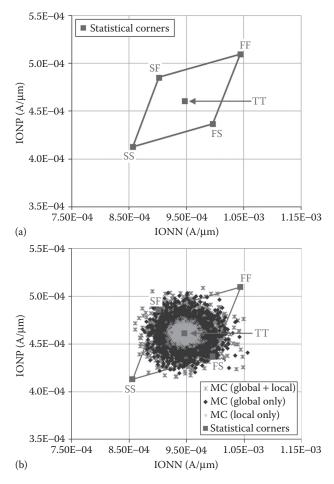

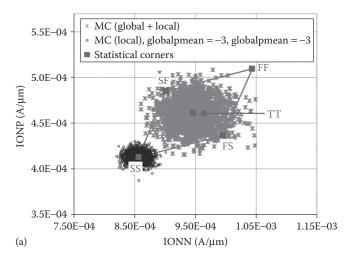

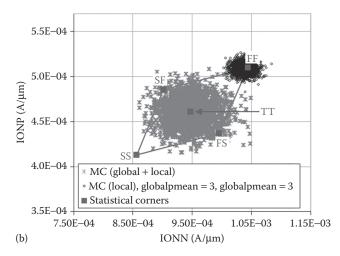

#### 1.2 Brief History of Compact Device Modeling