# Semiconductor Packaging

# Semiconductor Packaging

Materials

Interaction

and

Reliability

# Semiconductor Packaging

Materials

Interaction

and

Reliability

Andrea Chen Randy Hsiao-Yu Lo

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2012 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20110819

International Standard Book Number-13: 978-1-4398-6207-0 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

# Contents

| Pref            | face                                                                                        | X111     |

|-----------------|---------------------------------------------------------------------------------------------|----------|

| Aut             | thors                                                                                       | xv       |

| Part            | tial list of abbreviations, acronyms, and symbols                                           | xvii     |

|                 |                                                                                             |          |

|                 |                                                                                             |          |

| Sect            | tion I: Semiconductor packages                                                              |          |

| C1              |                                                                                             | 2        |

|                 | apter 1 History and background                                                              |          |

| 1.1             | Objectives                                                                                  |          |

| 1.2             | Introduction                                                                                |          |

| 1.3             | Brief history                                                                               |          |

|                 | 1.3.1 Hermetic packaging                                                                    |          |

|                 | 1.3.2 Plastic packaging                                                                     |          |

| 1.4             | Wire bonding process flow                                                                   |          |

| 1.5             | Flip-chip process flow comparison                                                           |          |

| 1.6             | Equipment                                                                                   |          |

| 1.7             | Material interactions                                                                       |          |

| Bibl            | liography                                                                                   | 9        |

| Cha             | antow? Package form factors and families                                                    | 11       |

| Cita<br>2.1     | apter 2 Package form factors and families  Objectives                                       |          |

| 2.1             | Introduction                                                                                |          |

| 2.2             |                                                                                             |          |

| 2.3<br>2.4      | Package outline standardizationLeaded package families                                      | 11<br>12 |

| ∠. <del>4</del> | 2.4.1 Dual lead package family                                                              |          |

| 2.5             |                                                                                             |          |

| 2.6             | Quad lead package familySubstrate-based package families                                    | 13<br>12 |

| 2.0             |                                                                                             |          |

| 2.7             |                                                                                             |          |

| 2.7             | Chip scale packages                                                                         |          |

|                 | <ul><li>2.7.1 Substrate-based chip scale packages</li><li>2.7.2 Quad flat no lead</li></ul> |          |

| <b>၁</b> 0      | · ·                                                                                         |          |

| 2.8             | Stacked-die package family                                                                  |          |

| 2.9             | Package-on-package and related variations                                                   | 1/       |

vi Contents

| 2.10   | Flip-c | hip packa   | ges                                          | 18 |

|--------|--------|-------------|----------------------------------------------|----|

|        |        |             | o scale packages                             |    |

|        |        |             |                                              |    |

| Char   | oter 3 | Surface-    | mount technology                             | 23 |

| 3.1    | Object | tives       |                                              | 23 |

| 3.2    |        |             |                                              |    |

| 3.3    |        |             |                                              |    |

| 3.4    |        |             | ng or "popcorning"                           |    |

| 3.5    | Surfac | e-mount     | packages: peripheral leads versus area array | 27 |

| 3.6    | Issues | with adv    | anced packaging                              | 29 |

| 3.7    |        |             | ture trends                                  |    |

|        |        |             | ee and halogen-free packaging                |    |

| Biblio |        |             |                                              |    |

| Char   | oter 4 | Other na    | ckaging needs                                | 33 |

| 4.1    |        |             | cruging needs                                |    |

| 4.2    |        |             |                                              |    |

| 4.3    |        |             | l bonding                                    |    |

| 4.4    | 1      |             |                                              |    |

| 4.5    |        |             | nodules                                      |    |

| 4.6    | 0      |             |                                              |    |

| 4.7    |        |             | ls for solar technology                      |    |

|        |        |             |                                              |    |

|        |        | D 1         | 1. 1.11.                                     |    |

| Secti  | on II: | Раскаде     | reliability                                  |    |

|        | oter 5 |             | ty testing                                   |    |

| 5.1    |        |             |                                              |    |

| 5.2    |        |             |                                              |    |

| 5.3    |        |             | iability tests                               |    |

|        | 5.3.1  | Precond     | ditioning conditions                         | 48 |

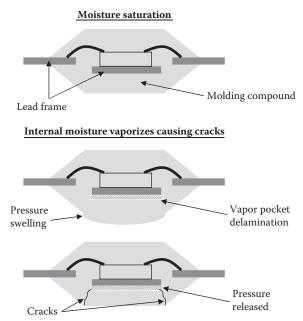

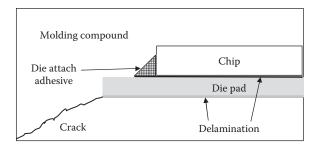

|        |        | 5.3.1.1     | Package failure mode: package crack or       |    |

|        |        |             | popcorning                                   |    |

|        | 5.3.2  |             | ature cycling and thermal shock              | 48 |

|        |        | 5.3.2.1     |                                              |    |

|        |        |             | cycling and thermal shock                    |    |

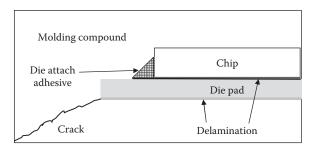

|        |        | 5.3.2.2     | Package failure mode: delamination           | 54 |

|        | 5.3.3  | High-te     | mperature storage life                       | 55 |

|        |        | 5.3.3.1     | Package failure mode: intermetallics         | 55 |

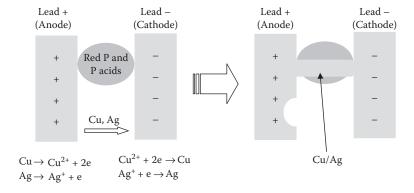

|        | 5.3.4  | Temper      | ature-humidity-bias tests                    | 55 |

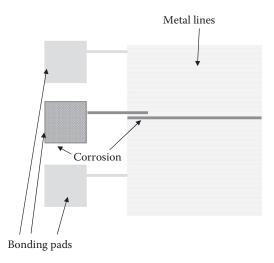

|        |        | 5.3.4.1     | Package failure mode: corrosion              |    |

| 5.4    | Limita | ations of r | eliability testing                           | 56 |

| Biblio | ograph | y           |                                              | 57 |

#### Section III: Materials used in semiconductor packaging

| Cha | pter 6  | Polymers | 5                                        | 61 |

|-----|---------|----------|------------------------------------------|----|

| 6.1 | Moldi   | ng compo | ounds                                    | 61 |

|     | 6.1.1   | Objectiv | ves                                      | 61 |

|     | 6.1.2   | Introdu  | ction                                    | 61 |

|     | 6.1.3   | Backgro  | ound                                     | 61 |

|     | 6.1.4   | Newer f  | formulations                             | 64 |

|     |         | 6.1.4.1  | Biphenyl                                 |    |

|     |         | 6.1.4.2  | Multifunctional                          |    |

|     |         | 6.1.4.3  | Aromatic resins                          |    |

|     | 6.1.5   | Technol  | ogy challenges                           | 66 |

|     |         | 6.1.5.1  | Moldability                              |    |

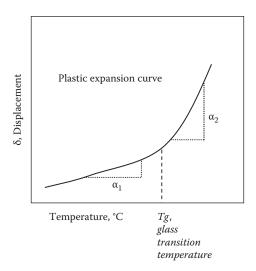

|     |         | 6.1.5.2  | Glass transition temperature             | 67 |

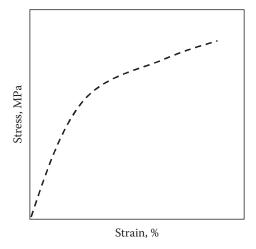

|     |         | 6.1.5.3  | Flexural modulus                         | 67 |

|     |         | 6.1.5.4  | Coefficient of thermal expansion         | 68 |

|     |         | 6.1.5.5  | Stress index                             | 68 |

|     | 6.1.6   | Failure  | modes associated with molding compounds  | 69 |

|     |         | 6.1.6.1  | Package cracking during solder reflow    | 69 |

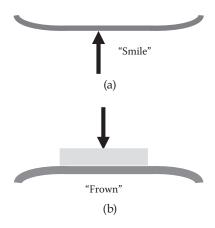

|     |         | 6.1.6.2  | Substrate postmold warpage               | 71 |

|     | 6.1.7   | Future o | developments                             | 72 |

|     |         | 6.1.7.1  | "Green" molding compounds and changes    |    |

|     |         |          | to flame retardant additives             | 72 |

|     |         | 6.1.7.2  | Molded underfill                         | 74 |

|     |         | 6.1.7.3  | High-density packaging                   | 74 |

|     |         | 6.1.7.4  | Compatibility with copper wire bonding   |    |

| 6.2 | Die att | ach adhe | sives                                    |    |

|     | 6.2.1   | Objectiv | /es                                      | 75 |

|     | 6.2.2   | Introdu  | ction                                    | 76 |

|     | 6.2.3   | Backgro  | ound                                     | 76 |

|     | 6.2.4   | Materia  | ls composition                           | 78 |

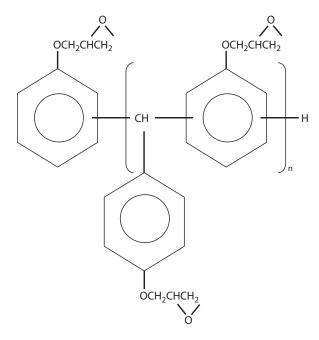

|     |         | 6.2.4.1  | Liquid epoxy resin                       | 78 |

|     |         | 6.2.4.2  | Silver flakes and other filler materials | 78 |

|     |         | 6.2.4.3  | Reactive epoxy diluents and solvents     | 78 |

|     |         | 6.2.4.4  | Catalysts and hardeners                  | 78 |

|     |         | 6.2.4.5  | Other additives                          | 78 |

|     | 6.2.5   | Materia  | ls analysis                              | 79 |

|     |         | 6.2.5.1  | Glass transition temperature             |    |

|     |         | 6.2.5.2  | Coefficient of thermal expansion         | 79 |

|     |         | 6.2.5.3  | Thixotropic index                        |    |

|     |         | 6.2.5.4  | Ionic purity                             | 80 |

|     | 6.2.6   | Reliabil | ity and performance                      |    |

|     |         | 6.2.6.1  | Outgassing                               | 81 |

|     |         | 6.2.6.2  | Resin bleed                              | 81 |

viii Contents

|       | 6.2.7    | Future o   | developments                                 | 82  |

|-------|----------|------------|----------------------------------------------|-----|

|       |          | 6.2.7.1    | Three-dimensional (3D) packaging             | 82  |

|       |          | 6.2.7.2    | Lead-free and restriction of hazardous       |     |

|       |          |            | substances (RoHS)                            | 83  |

|       |          | 6.2.7.3    | Compatibility with copper wire bonding       | 83  |

|       |          | 6.2.7.4    |                                              |     |

| 6.3   | Underf   | ill materi | ials                                         |     |

|       | 6.3.1    |            | /es                                          |     |

|       | 6.3.2    | Introdu    | ction                                        | 84  |

|       | 6.3.3    | What is    | underfill?                                   | 84  |

|       | 6.3.4    | The pur    | pose of underfill                            | 84  |

|       | 6.3.5    |            | ndard) underfill process                     |     |

|       | 6.3.6    |            | ll properties                                |     |

|       |          |            | Glass transition temperature                 |     |

|       |          | 6.3.6.2    | Coefficient of thermal expansion             |     |

|       | 6.3.7    |            | te underfill processes                       |     |

|       |          | 6.3.7.1    | "No-flow" underfill                          |     |

|       |          | 6.3.7.2    |                                              |     |

|       |          | 6.3.7.3    |                                              |     |

|       |          | 6.3.7.4    | Molded underfill                             |     |

|       | 6.3.8    |            | f research and development                   |     |

|       |          | 6.3.8.1    | Maintaining capillary flow as features sizes |     |

|       |          |            | shrinkshrink                                 |     |

|       |          | 6.3.8.2    | Compatibility with lead-free bump process    |     |

|       |          |            | steps, including for copper pillar bumps     | 90  |

|       | 6.3.9    | Failure    | modes                                        |     |

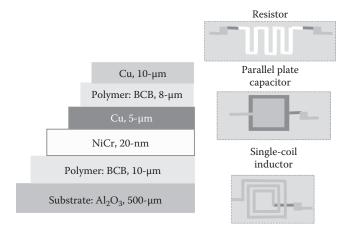

| 6.4   |          |            | ites                                         |     |

|       | 6.4.1    |            | /es                                          |     |

|       | 6.4.2    |            | ction                                        |     |

|       | 6.4.3    |            | ound                                         |     |

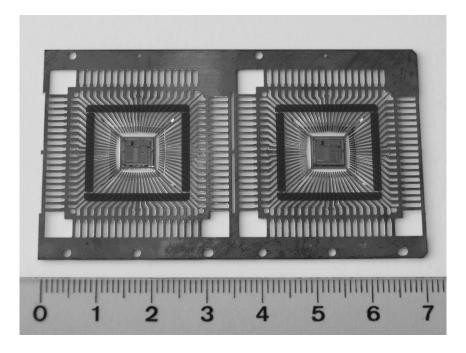

|       | 6.4.4    | 0          | d arrays and chip scale packages             |     |

|       | 0.1.1    | 6.4.4.1    | Microvias and high-density interconnect      | , _ |

|       |          |            | technology                                   | 93  |

|       | 6.4.5    | Future o   | developments                                 |     |

| Bibli |          |            |                                              |     |

| DIUII | ograpity |            |                                              | > 7 |

| Cha   | pter 7   | Metals     |                                              | 101 |

|       |          |            | at spreaders, and heat sinks                 |     |

|       | 7.1.1    |            | /es                                          |     |

|       | 7.1.2    |            | ction                                        |     |

|       | 7.1.3    |            | ames                                         |     |

|       | 7.1.4    |            | commonly used in lead frames and other       | 101 |

|       | 7.1.1    |            | ents                                         | 102 |

|       |          | 7.1.4.1    | Copper                                       |     |

|       |          | , .1.1.1   | Copper                                       | 102 |

Contents ix

|     |        | 7.1.4.2  | Alloy42                                     | 103 |

|-----|--------|----------|---------------------------------------------|-----|

|     |        | 7.1.4.3  | Aluminum                                    |     |

|     | 7.1.5  | Heat slu | gs, heat spreaders, and heat sinks          | 104 |

|     |        | 7.1.5.1  | Heat slugs or spreaders                     |     |

|     |        | 7.1.5.2  | Heat sinks                                  |     |

|     | 7.1.6  | Plating  | finishes                                    |     |

| 7.2 | Bondii |          |                                             |     |

|     | 7.2.1  | Objectiv | 7es                                         | 107 |

|     | 7.2.2  |          | ction                                       |     |

|     | 7.2.3  | Bonding  | g wires                                     | 108 |

|     |        | 7.2.3.1  | Gold                                        | 108 |

|     |        | 7.2.3.2  | Copper                                      | 108 |

|     |        | 7.2.3.3  | Aluminum                                    |     |

|     |        | 7.2.3.4  | Other                                       | 110 |

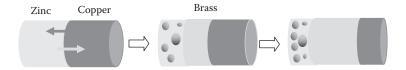

|     | 7.2.4  | Kirkend  | lall effect                                 | 111 |

|     |        | 7.2.4.1  | Gold-aluminum intermetallics and            |     |

|     |        |          | Kirkendall effect                           | 111 |

|     |        | 7.2.4.2  | Kirkendall effect for copper wire bonding   |     |

|     |        |          | on aluminum bond pads                       | 112 |

|     | 7.2.5  | Heat-aff | fected zone phenomenon in bonding wire      | 112 |

|     |        | 7.2.5.1  | How is the heat-affected zone created?      | 113 |

|     |        | 7.2.5.2  | Effect of heat-affected zone on loop height | 113 |

|     | 7.2.6  | Other re | eliability issues                           |     |

|     |        | 7.2.6.1  | Copper wire bonding and corrosion           |     |

|     | 7.2.7  | Materia  | ls analysis                                 |     |

|     |        | 7.2.7.1  | Visual inspection                           |     |

|     |        | 7.2.7.2  | Bond etching                                | 115 |

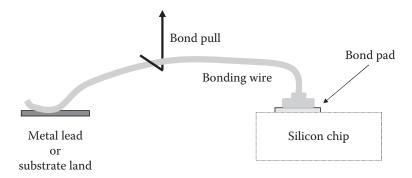

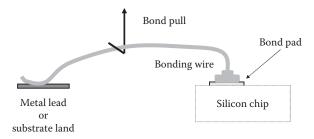

|     |        | 7.2.7.3  | Bond pull                                   |     |

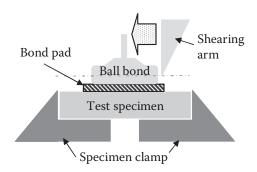

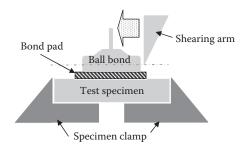

|     |        | 7.2.7.4  | Ball shear tests                            |     |

|     | 7.2.8  |          | developments                                | 115 |

|     |        | 7.2.8.1  | Copper wire bonding on nickel-palladium     |     |

|     |        |          | electroless plated bond pads                |     |

| 7.3 | Solder |          |                                             |     |

|     | 7.3.1  |          | ves                                         |     |

|     | 7.3.2  |          | ction                                       |     |

|     | 7.3.3  |          | f solders                                   |     |

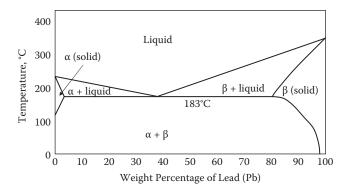

|     |        |          | Lead-based                                  |     |

|     |        |          | Lead-free                                   |     |

|     |        | 7.3.3.3  | Gold-based                                  |     |

| 7.4 |        |          |                                             |     |

|     | 7.4.1  |          | /es                                         |     |

|     | 7.4.2  |          | ction                                       |     |

|     | 7.4.3  |          | netallurgies                                |     |

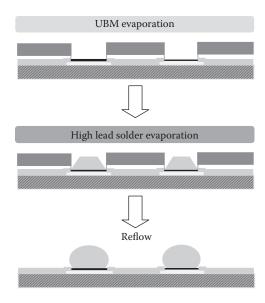

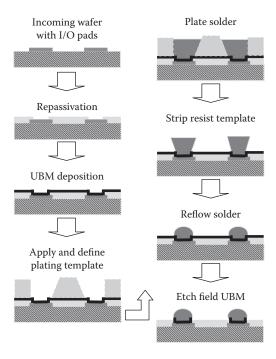

|     |        | 7.4.3.1  | "C4"                                        | 123 |

*x* Contents

|      |          | 7.4.3.2     | Electroplating                           | 123 |

|------|----------|-------------|------------------------------------------|-----|

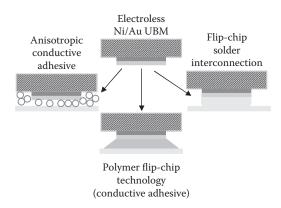

|      |          | 7.4.3.3     | Electroless (UBM) plating and screen/    |     |

|      |          |             | stencil printing solder                  | 125 |

|      |          | 7.4.3.4     | Lead-free bumping metallurgies           |     |

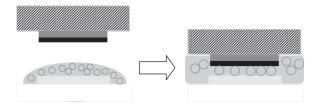

|      |          | 7.4.3.5     |                                          |     |

|      | 7.4.4    | Under-l     | oump metallurgy                          |     |

|      |          | 7.4.4.1     | Vacuum deposition                        |     |

|      |          | 7.4.4.2     |                                          |     |

|      |          | 7.4.4.3     |                                          |     |

|      | 7.4.5    | Technic     | al issues                                |     |

|      | 7.4.6    |             | directions                               |     |

| Bibl | iograph  |             |                                          |     |

| Cha  | pter 8   | Ceramics    | s and glasses                            | 133 |

| 8.1  |          |             |                                          |     |

| 8.2  | Introd   | uction      |                                          | 133 |

| 8.3  | Types    | of cerami   | cs used in semiconductor packaging       | 133 |

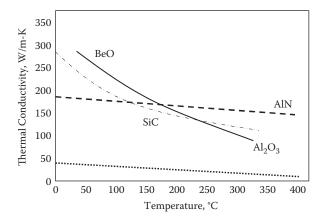

|      | 8.3.1    |             | ıa                                       |     |

|      | 8.3.2    | Beryllia    |                                          | 135 |

|      | 8.3.3    |             | um nitride                               |     |

|      | 8.3.4    | Silicon     | carbide                                  | 136 |

|      | 8.3.5    |             | itride                                   |     |

| 8.4  | Types    |             | s used in semiconductor packaging        |     |

|      | 8.4.1    |             | lled glass                               |     |

|      | 8.4.2    |             | kali borosilicate glass                  |     |

| Bibl |          |             |                                          |     |

| Sect | ion IV:- | —The fut    | ure                                      |     |

| Cha  | pter 9   | Trends a    | nd challenges                            | 143 |

| 9.1  |          |             |                                          |     |

| 9.2  |          |             |                                          |     |

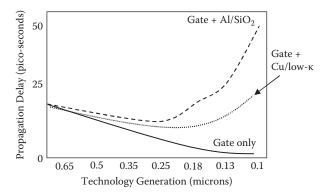

| 9.3  | Coppe    | er intercor | nnects and low-к dielectric materials    | 143 |

|      | 9.3.1    | Copper      | interconnects                            | 143 |

|      | 9.3.2    | Dielecti    | ic materials                             | 145 |

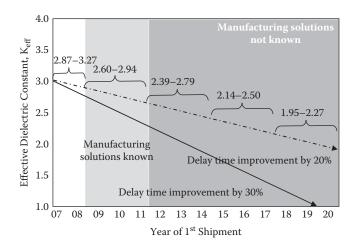

| 9.4  | Dielec   | tric const  | ant requirements at each technology node | 146 |

| 9.5  |          |             | nect and dielectric materials            |     |

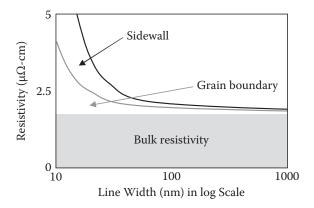

|      | 9.5.1    | Intercor    | nnects for <22 nm                        | 148 |

|      | 9.5.2    | Dielecti    | ric materials for ≥22 nm                 | 150 |

|      | 9.5.3    |             | ric materials for <22 nm                 |     |

| 9.6  | Future   | e packagii  | ng options                               | 151 |

|      | 9.6.1    |             | gning the chip with the package          |     |

|      | 9.6.2    |             | limensional (3D) integration             |     |

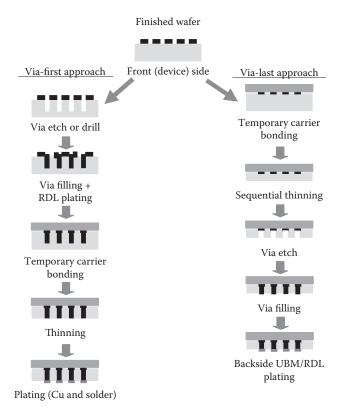

|       | 9.6.3   | Through-silicon vias                              | 151 |

|-------|---------|---------------------------------------------------|-----|

| Bibli |         | 7                                                 |     |

|       | 0 1 1   |                                                   |     |

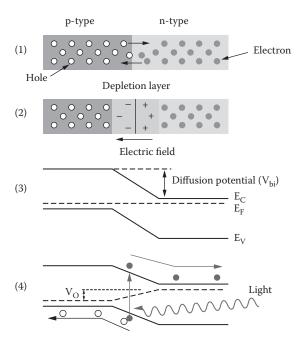

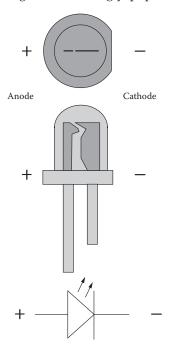

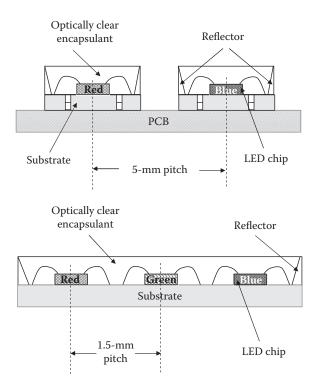

| Cha   |         | Light-emitting diodes                             |     |

| 10.1  | ,       | ives                                              |     |

| 10.2  |         | uction                                            | 155 |

| 10.3  |         | e characteristics of light-emitting diode (LED)   |     |

|       |         | ging needs                                        |     |

| 10.4  |         | ility requirements for LED packages               |     |

| Bibli | ography | 7                                                 | 161 |

| Glos  | sary    |                                                   | 163 |

|       |         | <i>J</i>                                          |     |

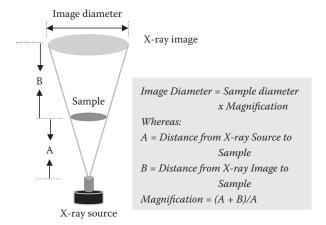

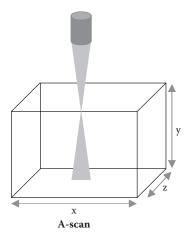

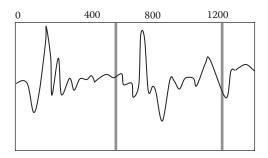

| App   | endix A | : Analytical tools                                | 167 |

| A.1   |         | uction                                            |     |

| A.2   |         | of analytical tools                               |     |

| A.3   |         | estructive tools and tests                        |     |

|       | A.3.1   | Introduction                                      |     |

|       | A.3.2   | Optical/visual inspection                         |     |

|       | A.3.3   |                                                   |     |

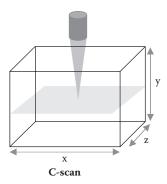

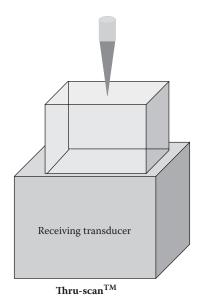

|       | A.3.4   | Scanning acoustic microscopy                      |     |

| Bibli | ography | 7                                                 |     |

| Арр   | endix B | : Destructive tools and tests                     | 177 |

| B.1   |         | uction                                            |     |

| B.2   |         | sulation                                          |     |

| B.3   |         | enetration                                        |     |

| B.4   |         | sectioning and polishing                          |     |

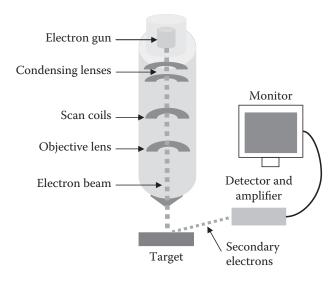

| B.5   |         | ing electron microscopy (SEM)                     |     |

| B.6   |         | mission electron microscopy (TEM)                 |     |

| B.7   |         | ical and elemental tests                          |     |

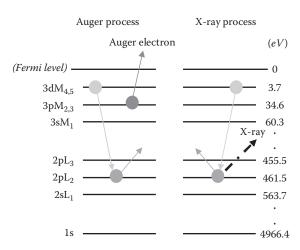

|       | B.7.1   | Auger electron spectroscopy (AES)                 | 180 |

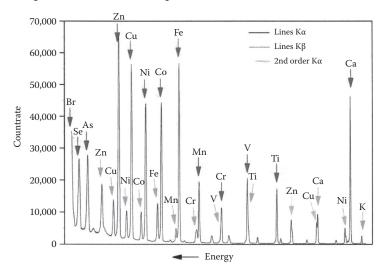

|       | B.7.2   | Energy-dispersive X-ray spectroscopy (EDS or EDX) | 181 |

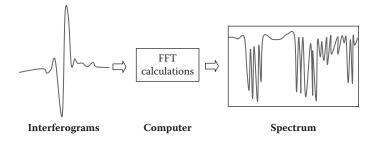

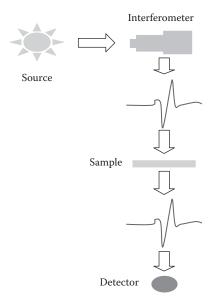

|       | B.7.3   | Fourier transform infrared spectroscopy (FTIR)    | 181 |

|       | B.7.4   | Secondary ion mass spectrometry (SIMS)            | 183 |

| B.8   | Other   | analytical techniques                             |     |

|       | B.8.1   | Bonding wire pull                                 | 183 |

|       | B.8.2   | Ball bond shear                                   |     |

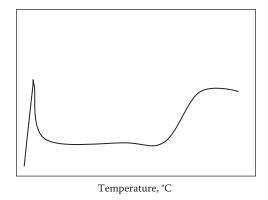

|       | B.8.3   | Differential scanning calorimetry (DSC)           |     |

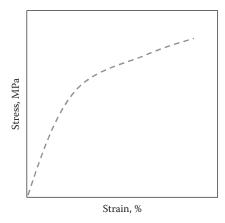

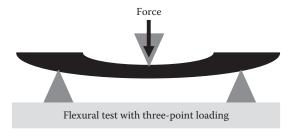

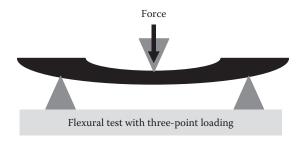

|       | B.8.4   | Flexural testing                                  |     |

| Bibli | ography | /                                                 | 186 |

| Inde  | X       |                                                   | 189 |

# Preface

Semiconductor packaging assembly and testing is an important manufacturing step necessary to create electronic products. The subject is not understood in much depth, as compared to a subject like circuit design. It is generally believed that this is due to the nature of the topic, as back-end processing of semiconductors is a multidisciplinary area, encompassing materials science, mechanical design, electrical layout and modeling, and many other engineering specialties. This book specifically addresses that shortcoming, especially in the area of materials used for packaging semiconductors and their interactions.

Simply put, semiconductor packages are not monolithic entities but are made up of many different components interlocked with the common goal of protecting the integrated circuit while allowing it to communicate with the outside world—the lead frame or substrate on which the chip sits upon, the die attach adhesive to glue the chip down, electrical connections made via metallic bonding wires or bond pad bumps for flip-chip attachment, and finally an epoxy molding compound to encapsulate everything for protection. And, those components are made up of very different materials: polymers, composites, metals, and various combinations of those categories. Understanding how the various materials behave and interact as they form the protective barrier for the delicate chip is key for making the package reliable and robust.

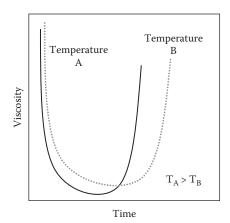

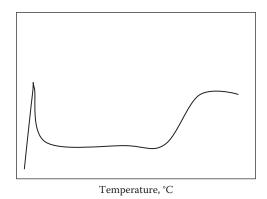

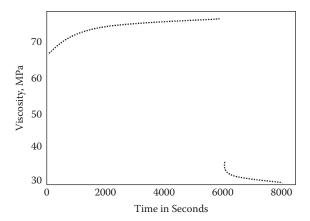

To gain these insights, a basic knowledge of material properties is necessary, along with determining which behaviors are important to package performance. That takes understanding how a given property is measured and why it is significant. For example, the measurement of viscosity versus time—a viscosity curve—in a molding compound or the length of the heat-affected zone in metallic wire used in thermosonic bonding eventually translates into a certain level of performance for manufacturing or reliability purposes for a given package.

From there, the next step is looking at how these properties of various packaging materials interact with one another and how to maximize their performance in regard to package integrity and reliability. Again, as an example, the length of the heat-affected zone in a bonding wire will help

*xiv* Preface

determine how high or how low the final loop height will be. In another example, a viscosity curve for a molding compound often acts as an indicator of its utility in manufacturing, by its ability to efficiently and completely fill cavities in a mold chase.

This book is focused on providing a fundamental understanding of the underlying physical properties that make up the materials used in a semiconductor package. By tying together the disparate elements that are essential to a semiconductor package, this volume hopes to convey the knowledge of how all the parts fit and work together to provide durable protection to the integrated circuit chip within as well as a means for the chip to communicate with the outside world.

### **Authors**

Andrea Chen received a B.S. in Materials Science and Engineering from University of California, Berkeley and a M.S. in Materials Engineering from Rensselaer Polytechnic Institute, New York. She started her career at National Semiconductor Corporation in the Package Technology group, working on various semiconductor packaging materials and reliability issues. Subsequently, she went to ChipPAC, Inc., with the Technology Development group, involved in low-cost flip-chip technology development. Currently, Chen works at Siliconware USA, Inc. (SPIL) as a technical marketing manager. To date, she has coauthored more than 30 papers and presentations.

Randy Hsiao-Yu Lo received his B.S. from National Taiwan University, Taiwan in 1979; M.S from Worcester Polytechnic Institute, Massachusetts in 1984; and Ph.D. from Purdue University, Indiana in 1990—all in the field of chemical engineering. He was at National Semiconductor Corporation from 1984 onward, eventually becoming senior engineering manager in the Package Technology group. Subsequently, he headed the Electronic Packaging Development group at ERSO/ITRI-Taiwan from 1997 to 1998. Then, he led the Siliconware Precision Industries Limited (SPIL) Research and Development group until 2000. Later that same year, he was appointed executive vice president and head of North America Sales and Marketing for Siliconware USA, Inc. In 2001, Lo was appointed president for Siliconware USA, Inc.—the position he currently holds. To date, he has coauthored more than 20 papers and presentations and is listed as coinventor on over 30 U.S. patents.

# Partial list of abbreviations, acronyms, and symbols

ACLV—autoclave

AES—Auger electron spectroscopy

AlN—aluminum nitride

$Al_2O_3$ —alumina, aluminum oxide

ASIC—application-specific integrated circuit

CMOS—complementary metal oxide semiconductor

CCD—charge coupled device

CSP—chip scale package

CTE—coefficient of thermal expansion

DIP—dual in-line (through-hole leads) package

DRAM—dynamic random access memory

DSC—differential scanning calorimetry

DSP—digital signal processor

EFO—electronic flame off

EIA—Electronics Industries Alliance

EDS or EDX—energy-dispersive X-ray spectroscopy

ENIG—"Electroless Nickel Immersion Gold"

ESD—electrostatic discharge

FAB—free air ball

FPGA—field programmable gate arrays

FTIR—Fourier transform infrared spectroscopy

HAST—highly accelerated stress test

HAZ—heat-affected zone

HDI—high-density interconnect

HTSL—high-temperature storage life

Hz—hertz, as in one cycle per second (1 Hz = 1 cycle per second)

IC—integrated circuit

IQA—incoming quality assurance

I/O—input-output

IR—infrared

κ—dielectric constant

LED—light-emitting diode

LTCC—low-temperature co-fired ceramic

MCM—multichip module

MCP—multichip package

MEMS—Micro Electro-Mechanical System

OSP—organic solderability preservative

PCB—printed circuit board

PGA—(through-hole) pin grid array packages

PLCC—plastic leaded chip carriers, with surface-mount J-leads

PoP—package-on-package

*ppm*—parts per million

PQFP—plastic quad flat pack

PTH—plated through-hole

RAM—random access memory

RGB—red-green-blue (LED lighting combination)

*SAM*—scanning acoustic microscopy

SEM—scanning electron microscopy

SIMS—secondary ion mass spectrometry

SiO<sub>2</sub>—silica, silicon dioxide

SO or SOP—small outline package, with gull-wing surface-mount leads

SOJ—small outline package, but with surface-mount J-leads

SMT—surface-mount technology

TAB—tape automated bonding

TEM—transmission electron microscopy

$T_{\rm g}$ —glass transition temperature

THB—temperature-humidity-bias reliability test

TMCL—thermal or temperature cycling reliability test

*TOP*—transistor outline package

TQFP—thin quad flat pack

TSOP—thin small outline package

YAG—ytterium-aluminum-garnet (phosphor used in LED production)

#### Bibliography

- C.A. Harper, *Electronic Packaging and Interconnection Handbook*, McGraw-Hill Professional, New York, 1991.

- L.T. Nguyen, R.H.Y. Lo, A.S. Chen, and J.G. Belani, "Molding Compound Trends in a Denser Packaging World II: Qualification Tests and Reliability Concerns," *IEEE Trans. on Reliability*, vol. 42, no. 4, 518–535, December 1993.

- S.L. Oon, "The Latest LED Technology Improvement in Thermal Characteristics and Reliability—Avago Technologies' Moonstone 3-in-1 RGB High Power LED," Avago Technologies White Paper, AV02-1752EN, March 17, 2010.

- M. Wright, "Internatix Launches New Red and Green LED Phosphors," *LEDs Magazine*, November 11, 2010.

## section one

# Semiconductor packages

### chapter one

# History and background

#### 1.1 Objectives

- Discover semiconductor packaging.

- Provide brief background and history of semiconductor packaging technology.

- Learn basic process steps involved in plastic semiconductor package assembly.

#### 1.2 Introduction

Semiconductor packaging is a middle link in electronics systems manufacturing, starting from wafer fabrication of multiple integrated circuits and proceeding all the way to final enclosure for the finished product. It must meet the demands of the steps prior to it, at the front end of production, and those steps that follow, through mounting on a printed circuit board and final systems integration. These demands tend to be contradictory, while at the same time, requirements for increased and better performance from the package are always increasing.

Simply put, a semiconductor package is a semiconductor chip enclosed or encapsulated to assure environmental protection, and it provides for a reliable means of interconnection to the next level of integration. The package is dubbed the *first level* of packaging, with the circuit board being the *second level* and the final enclosure the *third level*.

Specifically, a semiconductor package should protect the chip from mechanical stresses (vibration, falling from a height), environmental stresses (such as humidity and contaminants), and electrostatic discharge (also known as ESD) during handling and mounting onto a printed circuit board and beyond. In addition, the package is the mechanical interface for electrical testing, burn-in, and the next level of interconnection. Last, the package must also meet the chip's various performance requirements, encompassing the physical, mechanical, electrical, and thermal. Finally, the package must meet specifications for quality and reliability as well as be a cost-effective solution toward the final product. In all, semiconductor packages are an important part of any electronics system, though it is often neglected or treated as an afterthought—until there is a problem.

Therefore, this chapter addresses background information needed to understand the use and importance of the various materials and components used in semiconductor packaging.

#### 1.3 Brief history

Here is a brief description of the progression of semiconductor packages, from metal cans and ceramic packages in the early days to today's packages made up of lightweight organic materials. In the future, even more exotic materials may be commonplace in complex package structures.

#### 1.3.1 Hermetic packaging

As already mentioned, in the early days of the semiconductor industry, the majority, if not all, of semiconductor packages were ceramic based or metal cans. Given that the earliest adopters of semiconductors were the military and aerospace industries, hermetic packages offered the highest levels of reliability under any possible adverse operating conditions. By design, a hermetic seal prevents any contaminants, whether gases, liquids, or particulates, from reaching the sensitive and relatively delicate semiconductor chip surface within the package cavity. More details on hermetic packages are given in Chapter 2.

However, their robustness also had drawbacks. Hermetic materials tend to be costly and hard to manufacture and process, due to their hardness and brittle natures. The packages—the ceramic ones, especially—could be heavy and large, which meant the printed circuit board and overall enclosure had to also be large and heavy to support the weight. Finally, hermetic packages tend not to lend themselves to miniaturization. The semiconductor industry eventually turned to using organic materials and plastics, for both cost and weight savings, starting in the 1970s.

Though plastic package unit volumes now far surpass those for hermetic ones, they remain in use for applications that have demanding performance and environmental needs. Two applications where hermetic packaging still finds demand are light-emitting diode (LED) and Micro Electro-Mechanical System (MEMS) packaging, which is discussed in Chapter 4.

Many of the well-known and commonly used semiconductor packages that will be described shortly have both ceramic originators and organic successors. They include dual in-line, pin grid arrays, leaded chip carriers, and they all have ceramic and molding compound versions.

#### 1.3.2 Plastic packaging

The plastic version of the dual in-line packaging (DIP) family was introduced in the early 1970s and then proceeded to dominate the market for

plastic packages until the late 1980s, when surface-mount technology (SMT) arrived on the scene, with quad flat packs, small outline packages, and plastic leaded chip carriers.

To summarize the progress of package technology, through-hole packages like DIPs were the first plastic semiconductor packages to enter widespread use. "Through-hole" refers to the fact the package leads or pins went through holes in the printed circuit board to make their physical and electrical connections. Packages and their leads were both rather large in size. The next shift in technology came with the development of surfacemount technology, where the package leads were connected to lands on the circuit board, which allowed for both package body size and the leads to shrink in size. This is discussed in more detail in Chapter 3. More recently, the increasing pin counts forced the development of area array packages, like the ball grid array (BGA). The trend to ever-smaller, lighter, and thinner consumer electronic products was only achievable by further miniaturization, which drove the concept of chip scale packaging (CSP). The next step to reduce packaging cost and size was the approach of finishing the chip package directly on the wafer; thus, wafer-level packaging (WLP) was created. Going forward, this book will focus on plastic semiconductor packages grouped by interconnect method, whether by wire bonding or flip-chip attachment, and finally under wafer-level packaging.

Though in the past, packaging and interconnection technologies were not limiting factors in wringing maximum performance out of a device, demands from both the device and system ends has meant more and more focus is being placed on package technology as a limiting factor, and the industry is looking for ways to address these issues.

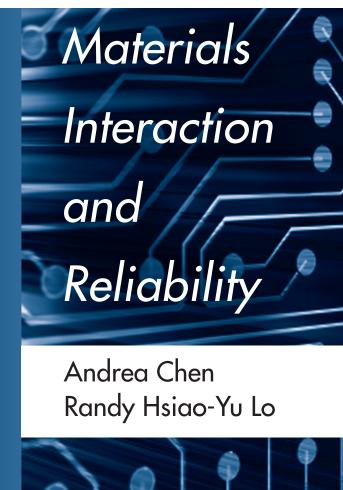

#### 1.4 Wire bonding process flow

The fundamental process flow for semiconductor packaging using wire bonding has remained relatively unchanged for the past 40 and more years, though the equipment and materials used have undergone considerable improvement and changes. Manufacturing operations have gone from manual, labor-intensive operations to highly automated, high-volume production. Materials are of higher overall quality and chemical purity, and they are engineered for specific properties and applications. Table 1.1 shows the process steps associated with wire-bonded packages, both plastic (such as for a plastic ball grid array) and hermetic (such as for ceramic dual-inline packages) types, and Figure 1.1 illustrates the process flow.

#### 1.5 Flip-chip process flow comparison

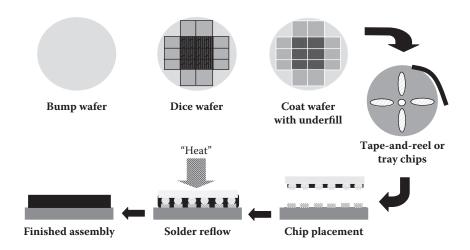

Table 1.2 compares the process steps changes going from a wire-bonded substrate package to one using a flip chip. In addition to starting with

| Plastic (Lead Frame) | Plastic (Laminate)               | Hermetic         |

|----------------------|----------------------------------|------------------|

| Wafer sort           | Wafer sort                       | Wafer sort       |

| Second optical       | Second optical                   | Second optical   |

| Wafer mount          | Wafer mount                      | Wafer mount      |

| Wafer sawing         | Wafer sawing                     | Wafer sawing     |

| Die attach           | Die attach                       | Die attach       |

| Wire bond            | Wire bond                        | Wire bond        |

| Third optical        | Third optical                    | Third optical    |

| Encapsulate (molding | Encapsulate (molding compound or | Lid seal         |

| compound)            | glob top)                        |                  |

| Dejunk               | Ball attach and reflow           | Leakage test     |

| Deflash              | Singulate                        | Marking          |

| Marking              | Ball inspection                  | _                |

| Plating              | Marking                          |                  |

| Trim and form        | Ç                                |                  |

| Final inspection     | Final inspection                 | Final inspection |

Table 1.1 Comparison of Process Steps between Package Types

Source: Adapted from National Semiconductor Corporation, Data Sheet: Semiconductor Packaging Assembly Technology, August 1999.

a bumped wafer, the major changes come in during the interconnection steps—die attach adhesive plus wire bond replaced pick-and-place plus reflow. Type of encapsulation is also different, with molding compound generally replaced by underfill.

Further discussion on underfill materials is given in Chapter 6, Section 6.3, and more information on wafer bumping will be presented in Chapter 7, Section 7.4.

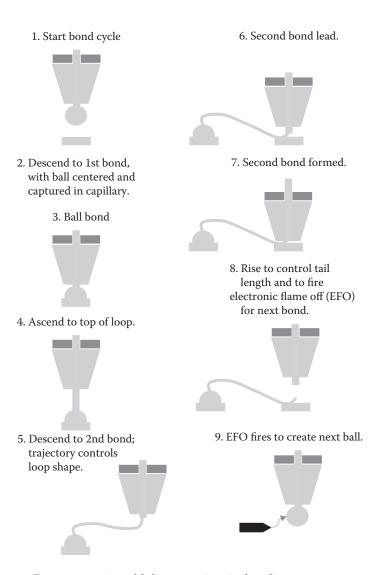

#### 1.6 Equipment

As an example, Figure 1.2 illustrates a transfer mold press used with molding compound to encapsulate plastic packages. Nearly all the steps shown in Table 1.2, which describe semiconductor package assembly and manufacturing, now use automated equipment for volume production—the die bonder, the wafer saw, and, of course, the wire bonder, to name a few examples.

#### 1.7 Material interactions

The heterogeneous components that make up a semiconductor package often differ wildly in physical properties, as shown in Table 1.3. The key is to find the most reasonable material set that is also cost-effective and manufacturable in high-volume assembly. These interactions will be discussed in detail in subsequent chapters.

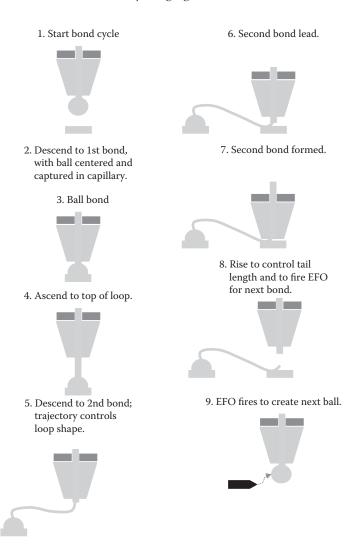

*Figure 1.1* Process steps in gold thermosonic wire bonding.

| Table 1.2 | Wire Bond versu   | ıs Flip-Chip |

|-----------|-------------------|--------------|

| Process F | lows for a Substr | ate Package  |

| Wire Bond    | Flip Chip                |

|--------------|--------------------------|

| Wafer        | Wafer                    |

| Dice         | Wafer bumping            |

| Die attach   | Dice                     |

| Cure         | Pick and place plus flux |

| Wire bonding | Reflow                   |

| Encapsulate  | Underfill encapsulation  |

| Ball attach  | Ball attach              |

| Mark         | Mark                     |

| System test  | System test              |

Source: Adapted from P. Elenius and L. Levine, "Comparing Flip-Chip and Wire-Bond Interconnection Technologies," Chip Scale Review, 81–87, July/August 2000.

Figure 1.2 Transfer mold press.

| Material | CTE<br>(ppm/°C) | Density<br>(g/cm³) | Thermal<br>Conductivity<br>(W/m*K) | Electrical<br>Resistivity<br>(μΩ-cm) | Tensile<br>Strength<br>(GPa) | Melting<br>Point<br>(°C) |

|----------|-----------------|--------------------|------------------------------------|--------------------------------------|------------------------------|--------------------------|

| Silicon  | 2.8             | 2.4                | 150                                | N/A                                  | N/A                          | 1430                     |

| Molding  |                 |                    |                                    |                                      |                              |                          |

| Compound | 18-65           | 1.9                | 0.67                               | N/A                                  | N/A                          | $165 (T_g)$              |

| Copper   | 16.5            | 8.96               | 395                                | 1.67                                 | 0.25-                        | 1083                     |

|          |                 |                    |                                    |                                      | 0.45                         |                          |

| Alloy42  | 4.3             | N/A                | 15.9                               | N/A                                  | 0.64                         | 1425                     |

| Gold     | N/A             | 19.3               | 293                                | 2.2                                  | N/A                          | 1064                     |

| Aluminum | 23.8            | 2.80               | 235                                | 2.7                                  | 83                           | 660                      |

| Eutectic |                 |                    |                                    |                                      |                              |                          |

| Tin-Lead |                 |                    |                                    |                                      |                              |                          |

| Solder   | 23.0            | 8.4                | 50                                 | N/A                                  | N/A                          | 183                      |

| Alumina  | 6.9             | 3.6                | 22                                 | N/A                                  | N/A                          | 2050                     |

| Aluminum |                 |                    |                                    |                                      |                              |                          |

| nitride  | 4.6             | 3.3                | 170                                | N/A                                  | N/A                          | 2000                     |

Table 1.3 Key Properties of Semiconductor Packaging Materials

Source: Adapted from National Semiconductor Corporation, Data Sheet: Semiconductor Packaging Assembly Technology, August 1999.

#### Bibliography

- M.G. Bevan and B.M. Romenesko, "Modern Electronic Packaging Technology," *Johns Hopkins APL Technical Digest*, vol. 20, no. 1, 22–33, 1999.

- P. Elenius and L. Levine, "Comparing Flip-Chip and Wire-Bond Interconnection Technologies," *Chip Scale Review*, 81–87, July/August 2000.

- K. Gilleo, B. Cotterman, and T. Chen, "Molded Underfill for Flip Chip in Package," HDI Magazine, June 2000.

- C.A. Harper, *Electronic Packaging and Interconnection Handbook*, McGraw-Hill Professional, New York, Chapter 6, 1991.

- National Semiconductor Corporation, *Data Sheet: Hermetic Packages*, August 1999. National Semiconductor Corporation, *Data Sheet: Semiconductor Packaging Assembly Technology*, August 1999.

- M. Osborne, "A Comprehensive Study of Fine-Pitch Bonding Reveals the Importance of Process Control," *Chip Scale Review*, March 2006.

- M. Töpper, "10th Anniversay Insights—AShort History of Wafer-Level Packaging," Advanced Packaging, April 2002.

- R.R. Tummala, "Electronic Packaging Research and Education: A Model for the 21st Century," *Johns Hopkins APL Technical Digest*, vol. 20, no. 1, 111–121, 1999.

### chapter two

# Package form factors and families

#### 2.1 Objectives

- List and categorize the different types of plastic semiconductor packages currently available on the market.

- Discuss the various failure modes plastic packages are subject to, and potential remedies.

#### 2.2 Introduction

The variety of plastic semiconductor packages available in the industry only continues to proliferate over time. Even as new types and form factors come into being, the established players do not disappear entirely, given their long, reliable history and cost-competitiveness when price and not performance is the primary factor for package selection. Table 2.1 shows the mature package families of dual in-line, small outline, and thin small outline packages still account for over 40% of semiconductor package units produced worldwide.

The increase in the number of package types matches the growth seen in the number and types of electronic products entering into common use. There are an ever-growing number of new applications for personal, healthcare, home, automotive, security, and entertainment systems. Advancement in package technology helped create the innovative solutions needed in new and future products.

#### 2.3 Package outline standardization

The industry association JEDEC—formed in 1958 as the Joint Electron Devices Engineering Council and now officially known as *JEDEC Solid State Technology Association*—regulates the standards and drawings for package configurations, outlines. JEDEC is the standardization arm of the *Electronics Industries Alliance (EIA)* and is a member of that umbrella organization. The comprehensive guide to all registered package outlines is in Publication 95 (JEP95), located on the JEDEC website.

| Package Type | Share, % |                   |

|--------------|----------|-------------------|

| SO           | 24.8     |                   |

| TSOP         | 13.4     |                   |

| SOT          | 7.6      |                   |

| DIP          | 5.3      |                   |

| DCA          | 7.7      |                   |

| WLP          | 4.2      |                   |

| FBGA/DSBGA   | 13.7     |                   |

| BGA          | 4.4      |                   |

| PGA          | 0.1      |                   |

| QFN          | 5.4      |                   |

| QFP          | 9.2      |                   |

| CC           | 0.8      |                   |

| DFN          | 3.5      |                   |

| Total        | 100      | 151 billion units |

Table 2.1 2007 Worldwide Integrated Circuit (IC)

Packaging Units by Package Family

Notes: SO, small outline package; TSOP, thin small outline package; SOT, small outline transistor; DIP, dual inline (through-hole leads) package; DCA, direct chip attach; WLP, wafer-level packaging; FBGA, fine pitch ball grid array/DSBGA, die-sized ball grid array; BGA, ball grid array; PGA, pin grid array packages; QFN, quad flat no lead; QFP, quad flat pack; CC, chip carrier; DFN, dual flat no lead.

Source: Adapted from Sandra Winkler, "Trends in IC Packaging and Multicomponent Packaging," IEEE SCV Components, Packaging and Manufacturing Technology Chapter, January 22, 2009.

#### 2.4 Leaded package families

As noted in Chapter 1, leaded packages have been used in the industry for decades. Even though the styles of packages have proliferated, they remain in wide use, especially for low-pin count parts and when cost is a primary consideration.

#### 2.4.1 Dual lead package family

Dual leaded packages are based on mature two-sided lead frame technology utilizing either PTH (plated through hole) or SMT (surface-mount technology). Within SMT grouping, there is *J lead*, which folds underneath the package body, and *gull wing*, where the leads fan away from the package body—configurations available for different SMT requirements. Lead counts range up to 86 pins.

There are a multitude of package types within the dual lead family, depending on lead type and shape, lead pitch, and body size and thickness. The plastic dual in-line package (or PDIP) uses PTH board mounting technology. Of the dual lead packages utilizing SMT, they are all variations of the small outline package (SOP), with the acronyms and names changing depending on whether the lead configuration is a J-lead (SOJ), or on the body profile and lead pitches.

#### 2.5 Quad lead package family

Quad leaded packages are based on mature four-sided lead frame technology utilizing SMT (surface-mount technology). Within SMT grouping, there are *J-lead* and *gull-wing* lead configurations available for different SMT requirements. Lead counts range up to 256 pins.

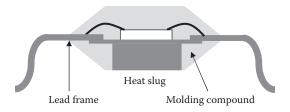

The quad packages with J-leads are generally known as plastic leaded chip carrier (PLCC) and have lead counts up to 84. Those with gull-wing leads are known as quad flat pack (QFP) packages. The QFP subgroup has several variations, depending on body thickness and lead pitch, with lead counts ranging up to 256. QFP packages are also available with thermal enhancement, such as an exposed heat spreader.

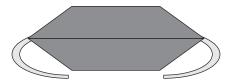

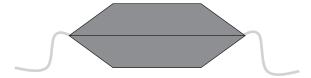

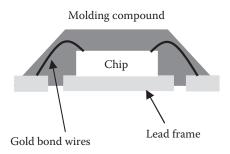

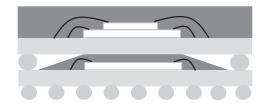

Figure 2.1 shows a J-lead plastic package in a cross-sectional view, and Figure 2.2 is of a gull-wing leaded plastic package.

#### 2.6 Substrate-based package families

At some point, an input/output (I/O) limitation was met with lead-frame-based packages. The leads could only be made so narrow before they became too fragile to handle during the assembly processes and final trim-and-form. To achieve greater I/O density to match the shrinking

Figure 2.1 J-lead leaded plastic package (not to scale).

*Figure 2.2* Gull-wing leaded plastic package (not to scale).

geometries of the chip, packages were developed to mimic printed circuit boards (PCBs), where denser electrical connections and routing could be met. Another advance was multitier wire bonding, to allow for staggered bonding lands to meet finer pitch densities. Finally, the use of organic substrates would allow flip-chip interconnect technology to become low(er) cost and more widely available for many different applications and devices.

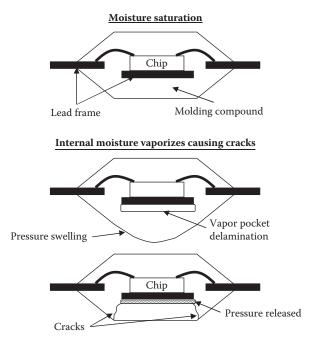

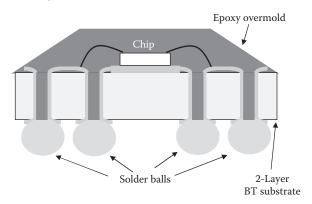

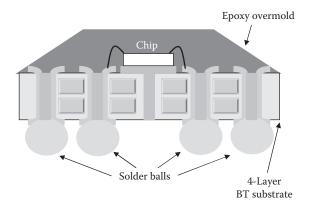

#### 2.6.1 Ball grid array package family

In a ball grid array (BGA) package, the chip is mounted to the top surface of a printed circuit board-type substrate instead of a metal lead frame. If the interconnection is wire bonding, the wires are connected to electrical traces on the substrate. Flip-chip interconnections may also be employed.

Compared to lead-frame packages, BGA packages offer superior electrical and thermal performance, higher interconnect density, and excellent surface-mount yields for high pin counts (usually above 256, which is generally the upper limit for QFPs).

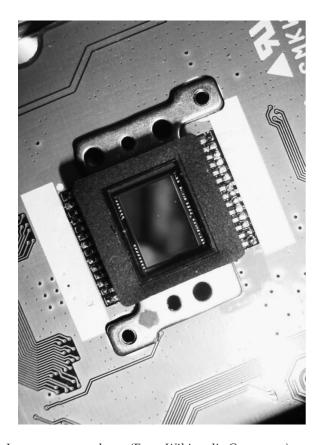

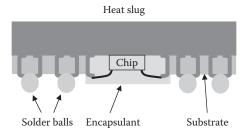

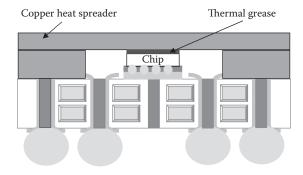

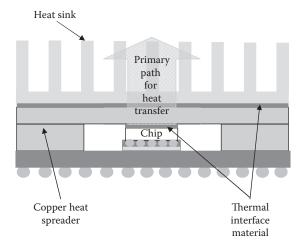

A BGA is a package technology that employs a solder ball grid array matrix to make electrical input and output connections to a printed circuit board. BGAs offers improved electrical and thermal operation through multiple routing layers such as ground and power planes. The package family includes cavity-up and cavity-down designs utilizing advanced substrate technologies, as well as optional heat spreaders and heat sinks when even higher thermal dissipation is a necessity.

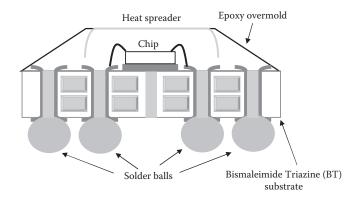

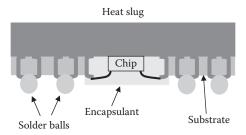

BGA packages are commonly used for high-performance applications such as microprocessors or controllers, application-specific integrated circuits (ASICs), digital signal processors (DSPs), gate arrays, and memory and computer chipsets. A thermally enhanced version is shown in

Figure 2.3 Thermally enhanced ball grid array (not to scale).

Figure 2.4 Cavity-down, thermally enhanced ball grid array (not to scale).

Figure 2.3, and Figure 2.4 shows a cavity-down version that provides both thermal and electrical improvements.

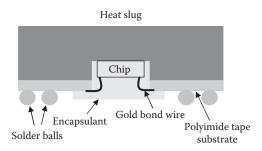

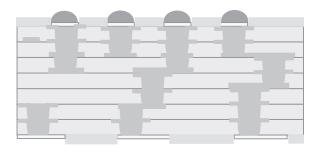

Polyimide tape can also be used as a substrate material. The tape requires attachment to a heat spreader for support as well as improved thermal performance. Drilling through the tape to allow solder ball connection to the heat spreader to act as a ground plane improves the electrical performance further, as illustrated in Figure 2.5.

#### 2.7 Chip scale packages

A chip scale package (CSP) is defined as a package where the bare die occupies 80% or more of the package area, so the profile can be a near-chip-size package outline. Electrical performance is enhanced due to shorter interconnections. CSPs may utilize lead frames or substrates, and the substrates may be rigid or flexible. The packages may have solder balls or simply metalized lands; the lead frame version may not have external leads, as in a quad flat no-lead package (see below). Also, interconnects may be wire bonds or flip chip (see Section 2.10, Flip-chip packages).

*Figure 2.5* Ball grid array using polyimide tape substrate (not to scale).

#### 2.7.1 Substrate-based chip scale packages

Essentially, substrate-based chip scale package technology is based on mature BGA technology and infrastructure, scaled down to small form factors. Chip scale packages must also meet design guidelines and rules regarding solder ball pitch and array patterns, as provided by JEDEC.

#### 2.7.2 Quad flat no lead

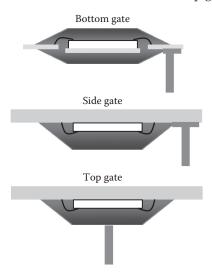

A quad flat no-lead (abbreviated as QFN) package is a plastic encapsulated lead-frame-based CSP with a lead pad on the bottom of the package to provide electrical interconnection with the printed circuit board. This package offers a small form factor with 60% size reduction compared with conventional QFP packages. It provides good electrical performance due to the short electrical path in the inner leads and wires. Electrical performance may be further enhanced by using a flip chip to shorten the interconnect path even further. The package also provides excellent thermal performance by an optional exposed die pad to provide an efficient heat path soldered on the circuit board. This small and light package with improved thermal and electrical performance makes QFNs suitable for portable communication and consumer products.

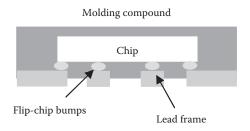

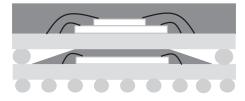

As already mentioned, interconnects may be made with wire bonding or with a flip chip. An example of the wire bond type is shown in Figure 2.6, and those of the flip-chip versions are shown in Figure 2.7.

Note that *punch type* and *map type* refer to both the molding method and subsequent singulation techniques. QFN packages may be molded individually and then punched out of the lead frame like other, traditional lead-frame packages. Or, an array of individual QFN packages may be molded as one large package and singulated subsequently by sawing.

Figure 2.6 Wire-bonded quad flat no lead (not to scale).

Figure 2.7 Flip-chip quad flat no lead (not to scale).

#### 2.8 Stacked-die package family

The stacked-die package is a package technology that stacks multiple die vertically in the same package. For example, multiple memory devices may sit on top of one another to increase memory density, or ASICs may be combined with memory chips. Compared to single-die packages, stacked-die packages combine several different functional devices or increase memory density in the same footprints as a single-die package. Stacked-die packages may include substrate-based and lead-frame-based types.

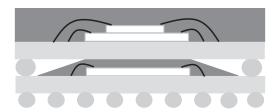

#### 2.9 Package-on-package and related variations

Multiple-package packages provide an alternative to multichip module solutions when known-good-die is not feasible. Multiple chips are integrated individually after undergoing functional tests within one package form factor. Rework of package on substrate is feasible to ensure the module yield. Figure 2.8 shows a variation on the multiple-packages-in-one called *package-on-package*, or PoP. In this example, the PoP vertically combines discrete memory (the top package) and logic chip (the bottom half) packages to save board space, lower overall pin count, and enhance electrical performance.

Figure 2.8 Package-on-package (not to scale).

## 2.10 Flip-chip packages

Flip-chip packages are not so much a stand-alone package form factor as a certain set of packages that share a common interconnect characteristic. Namely, the chip is not wire bonded for interconnect but instead flipped face-to-face with the substrate surface—hence the name *flip chip*—and the interconnection between the die and substrate is made through an array of bumps that are placed on the bonding pads of the die surface.

Flip-chip packages provide a solution for low to high pin count, high electrical performance demands from high-end memory, ASICs, and microprocessor applications where high frequency and high speed are required. Going from wire bonding to a flip-chip configuration makes it possible to jump into a higher pin count, and high electrical performance applications.

Flip-chip interconnections allow better electrical performance through lower inductances due to the shorter electrical path between the chip and the substrate. The array of bumps under the chip also allows the die to shrink in size, which can reduce wafer cost. The flip-chip structure also allows you to make power and ground connections to internal points on a die, resulting in better chip performance. To increase thermal performance, optional heat spreaders can be attached on the backside of the flipped die.

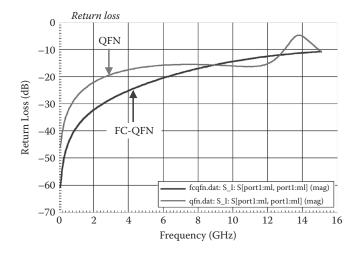

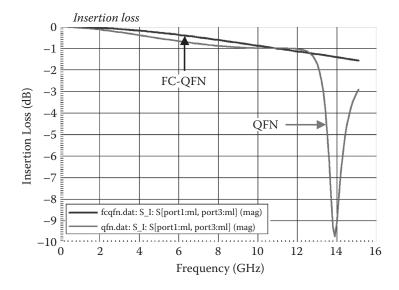

Types of packages employing a flip chip can be as small as 3 mm on a side CSPs up to mammoth 45 mm on a side BGAs. What is common among all of them is the need for enhanced electrical performance by shrinking the bond pad-to-lead distance. This can be seen in Figure 2.9, which shows the improvement in return loss in frequencies below 9 GHz between a wire-bonded quad flat no lead and a flip-chip version. Figure 2.10 shows the difference in insertion loss, which shows the flip-chip version has a bigger bandwidth range given that the wire bonded package shows 1 dB insertion loss at 10 GHz while the flip-chip package exhibits that behavior at 11 GHz.

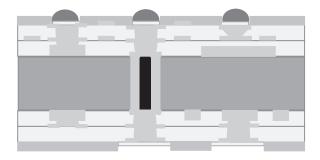

## 2.11 Wafer-level chip scale packages

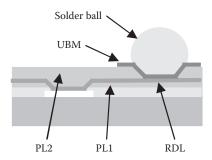

The concept of wafer-level packages emerged in the mid-1990s. Figure 2.11 shows a cross section from a wafer-level chip scale package. Note that redistribution is used to reroute connections from the peripheral bond pads to an area array to support the external solder ball connections.

A simplified process flow is described in Table 2.2. A finished wafer would undergo subsequent additional processing to make each individual chip a package: bond pad redistribution, additional layers of passivation, under bump metals, and finally the solder ball for external interconnection.

*Figure* **2.9** Return loss graphs comparing QFN and FC-QFN. (Reprinted with permission from Kevin Chang, Jen-Yuan Lai, Hanping Pu, Yu-po Wang, C.S Hsiao, Andrea Chen, and Randy H.Y. Lo, "Flip Chip Quad Flat No-Lead (FC-QFN)," *IWLPC* 2005, November 1, 2005.)

*Figure* **2.10** Insertion loss graphs comparing QFN and FC-QFN. (Reprinted with permission from Kevin Chang, Jen-Yuan Lai, Hanping Pu, Yu-po Wang, C.S Hsiao, Andrea Chen, and Randy H.Y. Lo, "Flip Chip Quad Flat No-Lead (FC-QFN)," *IWLPC* 2005, November 1, 2005.)

*Figure 2.11* Cross section of a wafer-level chip scale package (not to scale).

Table 2.2 Process Flow for Wafer-Level Chip Scale

|       | Packages                                      |

|-------|-----------------------------------------------|

| Steps | Description                                   |

| 1     | Finished wafer arrives from wafer fabrication |

| 2     | Passivation layer 1                           |

| 3     | Redistribution of bond pads                   |

| 4     | Passivation layer 2                           |

| 5     | Under bump metallurgy                         |

| 6     | Solder bumping                                |

| 7     | Solder bump reflow                            |

It is obvious that wafer-level packaging looks similar to a flip chip, and there is often confusion on whether a bare bumped chip is a wafer-level package or just a bare flip chip. Conventions seem to dictate that a wafer-level chip scale package is one that has spherical bumps on a grid pattern with a fixed, predetermined pitch, whereas as a bare flip chip would not adhere to these rules.

## Bibliography

- M.G. Bevan and B.M. Romenesko, "Modern Electronic Packaging Technology," Johns Hopkins APL Technical Digest, vol. 20, no. 1, 22–33, 1999.

- K. Chang, J.-Y. Lai, H. Pu, Y.-p. Wang, C.S. Hsiao, A. Chen, and R.H.Y. Lo, "Flip Chip Quad Flat No-Lead (FC-QFN)," *IWLPC 2005*, November 1, 2005.

- A. Chen, E. Feng, R. Lo, C.-C. Wu, T.D. Her, and C.Y. Lin, "The Future in 3-D Chip Scale Packaging," *SEMICON China* 2002, March 26–27, 2002.

- A. Chen, E. Feng, R. Lo, C.-C. Wu, and T.D. Her, "Recent Innovations in Stacked Die Packages," *KGD Workshop 2001*, September 12, 2001.

- Freescale Semiconductor, Application Note: Quad Flat Pack No-Lead (QFN), Micro Dual Flat Pack No-Lead (uDFN), AN1902, Rev. 4.0, September 2008.

- C.A. Harper, *Electronic Packaging and Interconnection Handbook*, McGraw-Hill Professional, New York, Chapters 6 and 9, 1991.

- M. Iyer, "Emerging Trends in Advanced Packaging," Semiconductor International, June 1, 2009.

- JEDEC, JEP95: Publication 95, www.jedec.org/download/pub95/default.cfm

- JEDEC, JEP95: Publication 95, Design Guide 4.18: Wafer Level Ball Grid Arrays (WLBGA), Issue A, September 2004.

- JEDEC, JEP95: Publication 95, Design Guide 4.6: Fine-Pitch, Rectangular Ball Grid Array Package (FRBGA), Issued, April 2005.

- JEDEC, JEP156: Chip-Package Interaction—Understanding, Identification and Evaluation, March 2009.

- R.H.Y. Lo and C.-C. Wu, U.S. Patent No. 6,507,120: Flip Chip Type Quad Flat Non-Leaded Package, January 14, 2003.

- R. Mahajan, K. Brown, and V. Atluri, "The Evolution of Microprocessor Packaging," Intel Technology Journal, Q3, 1–10, 2000.

- Maxim Integrated Products, Application Note 4002: Understanding Flip-Chip and Chip-Scale Package Technologies and Their Applications, April 18, 2007.

- National Semiconductor, Application Note 1126: BGA (Ball Grid Array), August 2003.

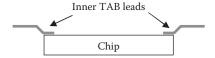

- P.J.C. Normington, "Patent Review: Patent Illustrates a New Use for Old Technology—Tape Automated Bonding," *Chip Scale Review*, July 2003.

- Siliconware Precision Industries Ltd., www.spil.com.tw/

- M. Töpper, "10th Anniversay Insights—A Short History of Wafer-Level Packaging," Advanced Packaging, April 2002.

- S. Winkler, "Trends in IC Packaging and Multicomponent Packaging," *IEEE SCV Components, Packaging and Manufacturing Technology Chapter*, January 22, 2009.

## chapter three

# Surface-mount technology

## 3.1 Objectives

- Provide a brief overview of semiconductor packages used in surfacemount technology of printed circuit boards.

- Discuss how issues particular to surface-mount technology affect semiconductor packages.

- Touch upon future developments in the area of surface-mount technology.

#### 3.2 Introduction

Surface-mount technology (SMT) refers to how various semiconductors, passives, and other components are attached to a printed circuit board (PCB), to both the top and bottom surfaces. In the beginning of the electronics industry, both packages and PCBs were relatively large in scale. Through-hole packages prevalent in the early days were called that because their leads fit into the holes drilled through the PCBs to connect power, ground, and circuitry connections.

In time, the demands of continual miniaturization of electronic products meant the boards inside them had to shrink, along with the chips and components. To save space and increase device density, the much-smaller lead area of surface-mount packages supplanted that of through-hole packages. For example, the lead pitch of a small outline package or a quad flat pack is half that or more compared to a plastic dual in-line (through-hole) package, at 1.27 mm or 1.00 mm versus 2.54 mm for the older technology. And not just for semiconductors but also for discrete devices, which lost their axial wire leads jutting out of cylindrical bodies to be replaced by much-smaller rectangular bricks with metalized end caps. Table 3.1 presents a comparison of package types and dimensions.

However, the transition from through-hole mounting technology to surface mount proved to have many challenges, not the least of which was the stress imposed on the semiconductor packages, to the point their reliability was reduced or even damaged. This chapter discusses those issues and subsequent solutions developed.

|                           |                    |                      | Body                 |                    |

|---------------------------|--------------------|----------------------|----------------------|--------------------|

| Package Type              | Pin Pitch          | Pin Length           | Thickness            | Body Width         |

| Plastic dual in-line      | 2.54 mm            | 3.17 mm              | 4.06 mm              | 7.62 to 22.9<br>mm |

| Small outline             | 1.27 mm            | 0.76 mm <sup>a</sup> | 2.49 mm              | 3.94 to 7.62<br>mm |

| Plastic quad<br>flat pack | 1.00 to 1.27<br>mm | 0.76 mm*             | 2.41 mm and<br>below | Variable           |

Table 3.1 Comparison of Through-Hole and Surface-Mount Package Types

Source: Adapted from Richard D. Skinner, Ed., Basic Integrated Circuit Technology Reference Manual, Integrated Circuit Engineering Corporation, Section 3: Packaging, 1993, figure 3-10.

## 3.3 Background

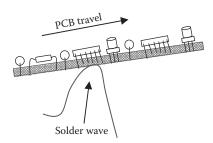

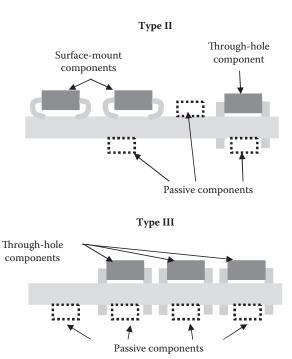

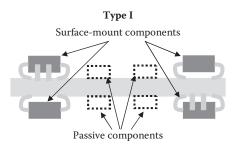

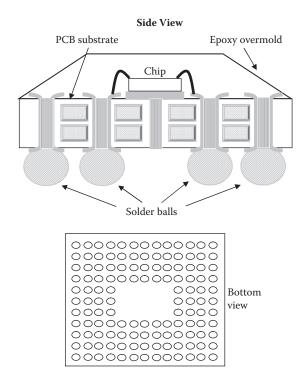

One major stumbling block was discovered when PCB mounting went from through-hole to surface mount, in the solder reflow step. In the days of through-hole packages and mounting, the majority of components were attached to one side of the board and the PCBs passed through a wave soldering machine, where molten eutectic tin-lead (Sn-Pb) solder was pushed along the boards backside, to wick up the through-holes to weld the package leads to the board, as illustrated in Figure 3.1. Generally, only passive components might be mounted on the bottom side and directly exposed to the solder wave, as the general wisdom advised not exposing active devices to molten solder. Having passive components only on the bottom side and through-hole active components is now generally known in the industry as a Type III SMT assembly, as shown in Figure 3.2. And while the molten metal was at least 183°C—the melting point for eutectic Sn-Pb solder—semiconductor packages unlikely saw peak temperatures very close to that level, insulated as they were by the thickness of the PCB. So, the thermal stresses experienced by the components were relatively benign.

*Figure 3.1* Wave soldering through-hole components.

<sup>&</sup>lt;sup>a</sup> Solderable length.

*Figure 3.2* A printed circuit board populated with through-hole and surface-mount components (Type II and Type III).

But when PCB technology moved to surface mount, a number of details changed in the solder reflow process. Table 3.2 shows the process steps for mixed assemblies of through-hole and surface-mount packages, also illustrated in Figure 3.2 and generally referred to as a Type II SMT assembly. Boards now had parts mounted on both sides, so it was more difficult to use wave soldering as an attachment process, because there are few, if any, through-holes left. Also, the components would risk being "washed" off by the molten solder, even with the package body attached to the board with heat-resistant adhesive. Instead, solder reflow would be achieved through convection heating, at first through vapor phase ovens and nowadays by infrared (IR) heat. The process flow is shown in Table 3.3. This also meant the packages would experience the same temperature excursions as the leads mounted to the PCB. A PCB with only SMT components is called a Type I SMT assembly and is illustrated in Figure 3.3. In all, the thermal stresses on the components and packages increased considerably with the move to SMT.

Given the increased thermal stresses, the bill of materials (BOM) that had served well through-hole mounting began to fail with the change to

## Table 3.2 Typical Attachment Process Flow for Mix of Through-Hole and Surface-Mount Components

- 1. Insert leaded components

- 2. Invert printed circuit board

- 3. Apply adhesive

- 4. Place surface-mount components

- 5. Cure adhesive

- 6. Invert board

- 7. Wave solder

- 8. Clean (if necessary)

- 9. Electrical test

Source: Adapted from Intel Corporation, Intel® Manufacturing Enabling Guide, Chapter 1, May 2010, figure 1-2.

#### Table 3.3 Typical Attachment Process Flow for Surface-Mount Components Only

- 1. Screen print solder paste on first side

- 2. Place components

- 3. Dry solder paste

- 4. Reflow solder

- (If populating a double-sided board, continue to step 5. Otherwise, skip to step 10.)

- 5. Invert printed circuit board

- 6. Screen print solder paste on second side

- 7. Place components

- 8. Dry solder paste

- 9. Reflow solder

- 10. Clean (if necessary)

- 11. Electrical test

Source: Adapted from Intel Corporation, Intel® Manufacturing Enabling Guide, Chapter 1, May 2010, figure 1-3.

*Figure 3.3* A printed circuit board populated with surface-mount components only (Type I).

SMT. The main phenomenon associated with the change is called *package cracking* and was nicknamed *popcorning*.

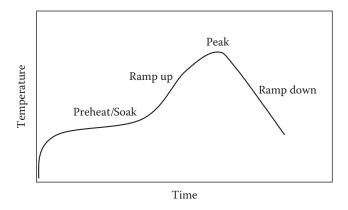

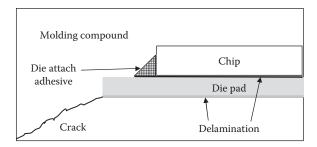

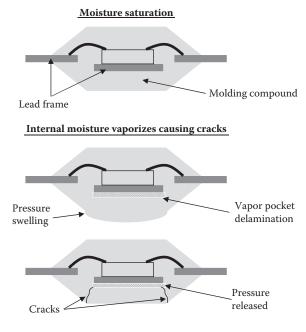

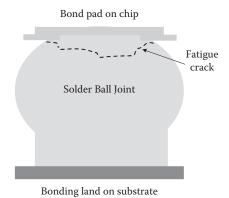

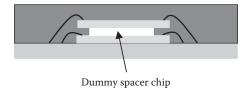

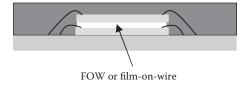

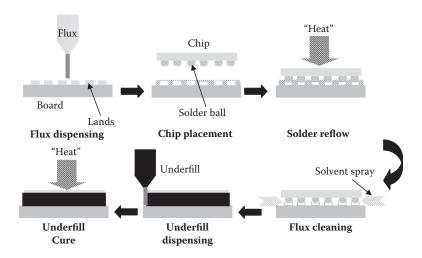

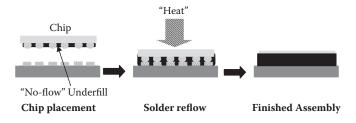

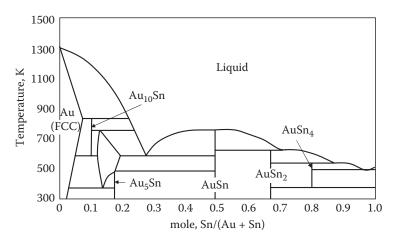

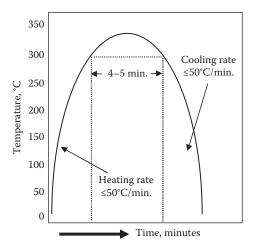

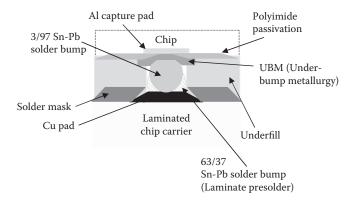

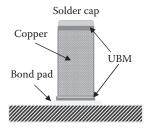

## 3.4 Package cracking or "popcorning"